本文來自格隆匯專欄:半導體行業觀察

近年來,因為傳統的晶體管微縮方法走向了末路,於是產業便轉向封裝尋求提升芯片性能的新方法。例如近日的行業熱點新聞《打破Chiplet的最後一道屏障,全新互聯標準UCIe宣吿成立》,可以説把Chiplet和先進封裝的熱度推向了又一個新高峯?

那麼為什麼我們需要先進封裝呢?且看Yole解讀一下。

為什麼我們需要高性能封裝?

隨着前端節點越來越小,設計成本變得越來越重要。高級封裝 (AP) 解決方案通過降低成本、提高系統性能、降低延遲、增加帶寬和電源效率來幫助解決這些問題。

高端性能封裝平台是 UHD FO、嵌入式 Si 橋、Si 中介層、3D 堆棧存儲器和 3DSoC。嵌入式硅橋有兩種解決方案:台積電的 LSI 和英特爾的 EMIB。對於Si interposer,通常有台積電、三星和聯電提供的經典版本,以及英特爾的Foveros。EMIB 與 Foveros 結合產生了 Co-EMIB,用於 Intel 的 Ponte Vecchio。同時,3D 堆棧存儲器由 HBM、3DS 和 3D NAND 堆棧三個類別表示。

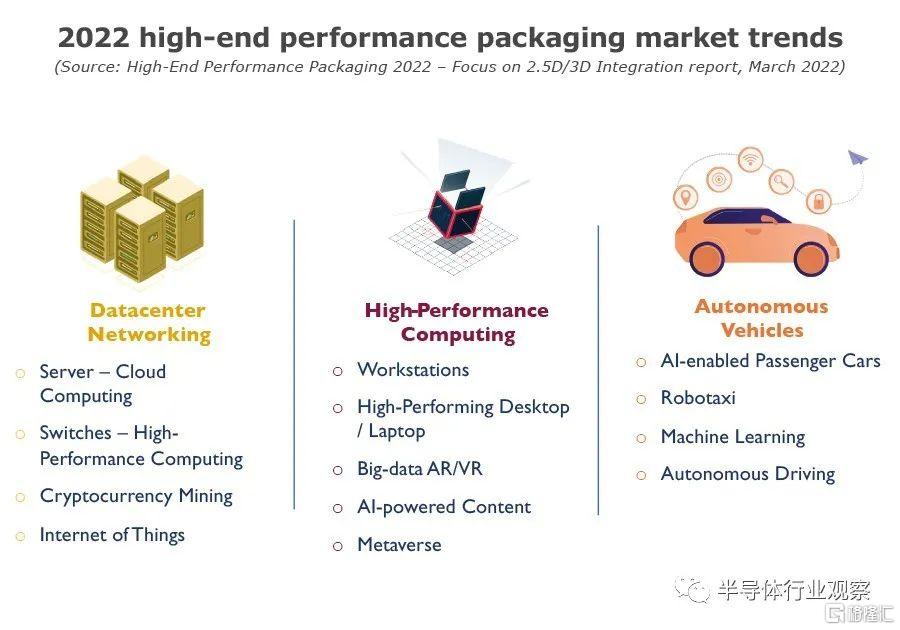

數據中心網絡、高性能計算和自動駕駛汽車正在推動高端性能封裝的採用,以及從技術角度來看的演變。今天的趨勢是在雲、邊緣計算和設備級別擁有更大的計算資源。因此,不斷增長的需求正在推動高端高性能封裝的採用。

高性能封裝市場規模?

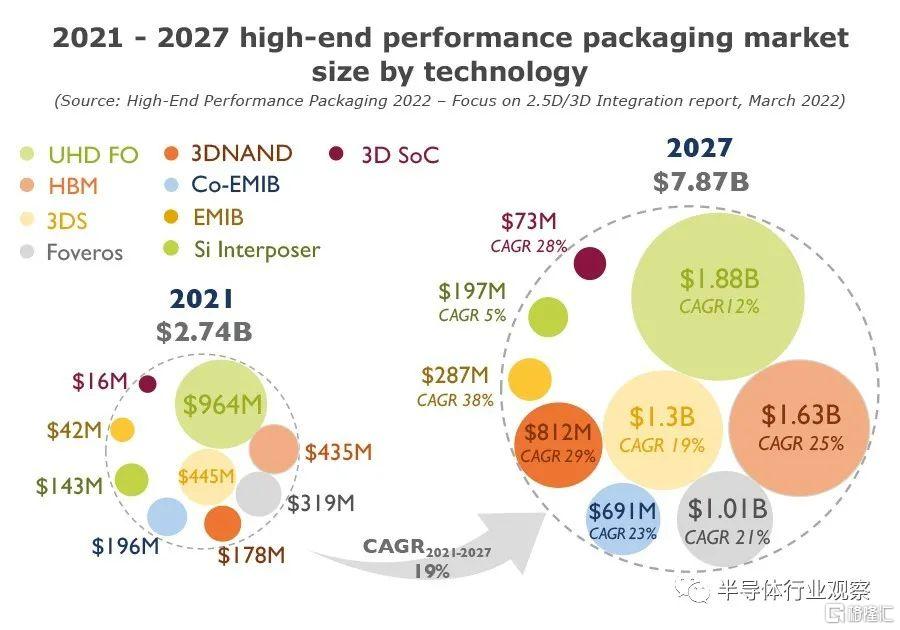

據Yole預測,到 2027 年,高性能封裝市場收入預計將達到78.7億美元,高於 2021 年的27.4億美元,2021-2027 年的複合年增長率為 19%。到 2027 年,UHD FO、HBM、3DS 和有源 Si 中介層將佔總市場份額的 50% 以上,是市場增長的最大貢獻者。嵌入式 Si 橋、3D NAND 堆棧、3D SoC 和 HBM 是增長最快的四大貢獻者,每個貢獻者的 CAGR 都大於 20%。

由於電信和基礎設施以及移動和消費終端市場中高端性能應用程序和人工智能的快速增長,這種演變是可能的。高端性能封裝代表了一個相對較小的業務,但對半導體行業產生了巨大的影響,因為它是幫助滿足比摩爾要求的關鍵解決方案之一。

誰是贏家,誰是輸家?

2021 年,頂級參與者為一攬子活動進行了大約116億美元的資本支出投資,因為他們意識到這對於對抗摩爾定律放緩的重要性。

英特爾是這個行業的最大的投資者,指出了35億美元。它的 3D 芯片堆疊技術是 Foveros,它包括在有源硅中介層上堆疊芯片。嵌入式多芯片互連橋是其採用 55 微米凸塊間距的 2.5D 封裝解決方案。Foveros 和 EMIB 的結合誕生了 Co-EMIB,用於 Ponte Vecchio GPU。英特爾計劃為 Foveros Direct 採用混合鍵合技術。

台積電緊隨其後的是 30.5億美元的資本支出。在通過 InFO 解決方案為 UHD FO 爭取更多業務的同時,台積電還在為 3D SoC 定義新的系統級路線圖和技術。其 CoWoS 平台提供 RDL 或硅中介層解決方案,而其 LSI 平台是 EMIB 的直接競爭對手。台積電已成為高端封裝巨頭,擁有領先的前端先進節點,可以主導下一代系統級封裝。

三星擁有類似於 CoWoS-S 的 I-Cube 技術。三星是 3D 堆棧內存解決方案的領導者之一,提供 HBM 和 3DS。其 X-Cube 將使用混合鍵合互連。

ASE 估計為先進封裝投入了 20 億美元的資本支出,是最大也是唯一一個試圖與代工廠和 IDM 競爭封裝活動的 OSAT。憑藉其 FoCoS 產品,ASE 也是目前唯一具有 UHD FO 解決方案的 OSAT。

其他OSAT 不具備在先進封裝競賽中與英特爾、台積電和三星等大公司並駕齊驅的財務和前端能力。因此,他們是追隨者。