本文來自格隆匯專欄:半導體行業觀察

通過在光刻圖案的分辨率上提供階躍函數增加的保真度,EUV光刻從根本上推動了半導體行業向前發展。然而,分辨率的提高並不是免費的。許多伴隨的進步也不得不帶來多個方面的變化,進而導致EUV 成本的提升。這些變化包括掩模生產、薄膜、沉積、蝕刻、硬掩模和光刻膠。雖然 EUV本身由 ASML 主導,但這種轉變已經在製造過程中的相鄰步驟(尤其是光刻膠行業)引發了一場價值數十億美元的高風險戰鬥。

日本長期以來一直在該領域佔據主導地位,東京電子擁有 EUV 光刻膠塗布機和顯影劑(photoresist coaters 和developers) 100% 的份額。由於他們在這個領域的壟斷地位,這讓他們在該市場以及蝕刻和清潔方面相關領域取得的年收入高達50億美元!此外,其他日本公司早已以約 75% 的市場份額壟斷了光刻膠市場。JSR 和 Tokyo Ohka Kogyo就是其中的領先者。他們提供了絕大多數專門用於 EUV 的化學放大(chemically amplified photoresist )光刻膠。然而,這些市場正受到 Lam Research 的衝擊。

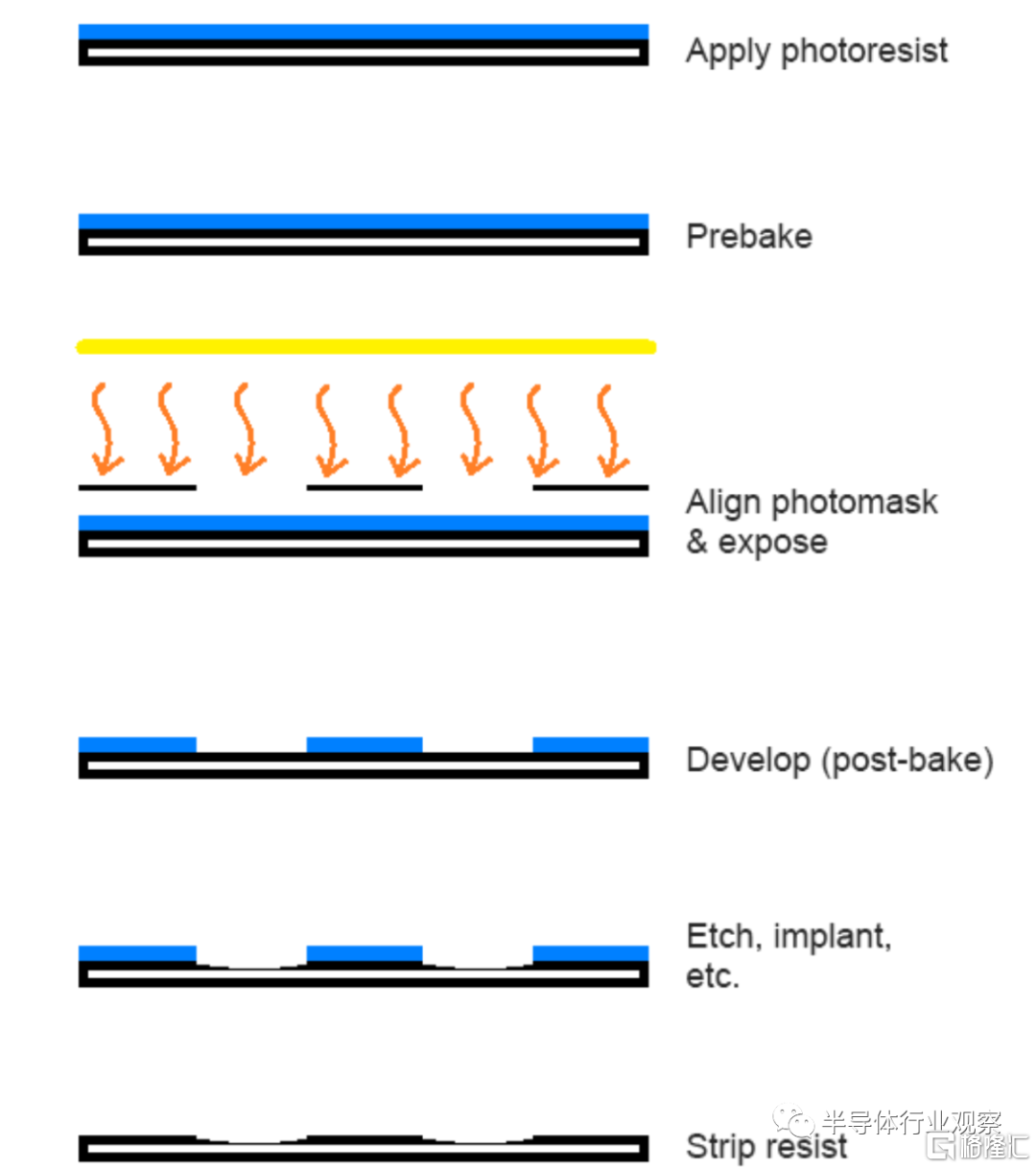

在深入探討即將到來的光刻膠戰爭的細節之前,讓我們簡單概述一下光刻圖案化過程。這一切都從清潔晶圓開始,這個步驟是爲了確保晶圓上沒有異物,如微小的灰塵分子或先前工藝中的殘留化學品。

在更高級的節點中,在光刻工藝之前,會有一些底層、中間層和硬掩模沉積在晶圓上。完成此沉積是爲了更準確地控制最終蝕刻,這是另一個話題。

最簡單的光刻形式將稱爲使用溼光刻膠(wet photoresist)的單一圖案化。清洗後的晶圓被放入東京電子塗布機和顯影劑中。該工具在硅片頂部沉積化學放大抗蝕劑 (CAR)。CAR 懸浮在液體溶液中,硅片以極快的速度旋轉以塗覆硅片。旋轉過程還通過離心力去除大部分液體,並留下一層薄薄的光刻膠。還進行了稱爲預烘烤的過程,以烤乾最後一點液體,並在某些情況下以化學方式爲即將進行的反應準備光刻膠。

隨後,硅片進入 ASML的光刻工具,然後通過掩模將光線照射到光刻膠上,並在那裏引起化學反應。之後,晶圓被送回到東京電子塗布機/顯影工具清洗,使用顯影劑洗掉光刻膠。如果這種光刻膠是正性的,那麼曝光的光刻膠會發生反應並變成溶劑,這樣它就可以被洗掉。如果是負的,曝光的光刻膠反應不再是溶劑,未曝光的光刻膠被洗掉。這僅適用於光刻工藝,除此之外還存在其他相關工藝,例如多圖案技術、蝕刻和間隔物,但讓我們今天關注光刻工藝。

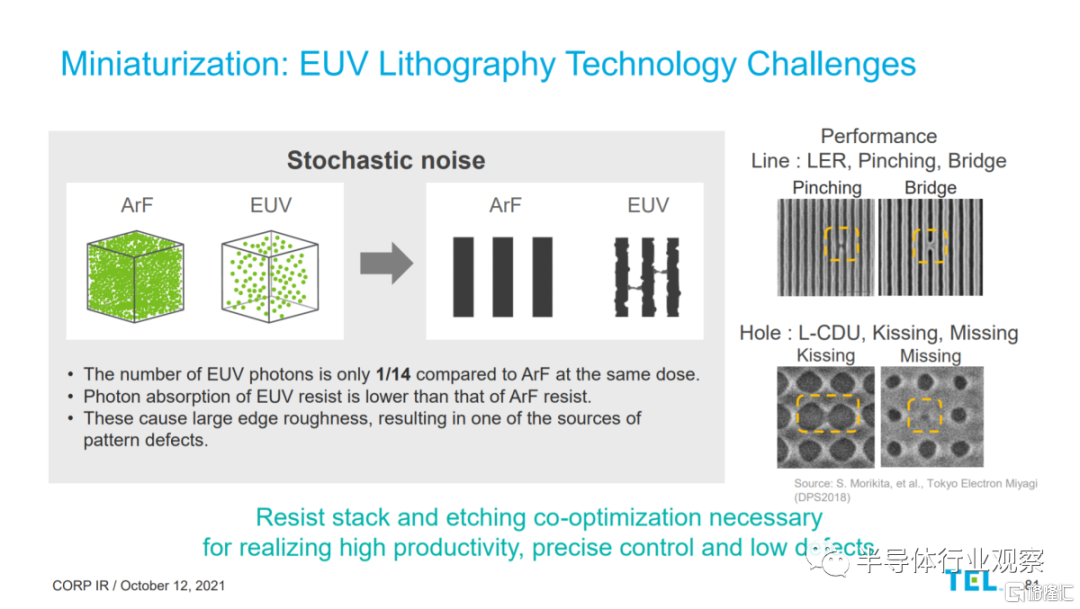

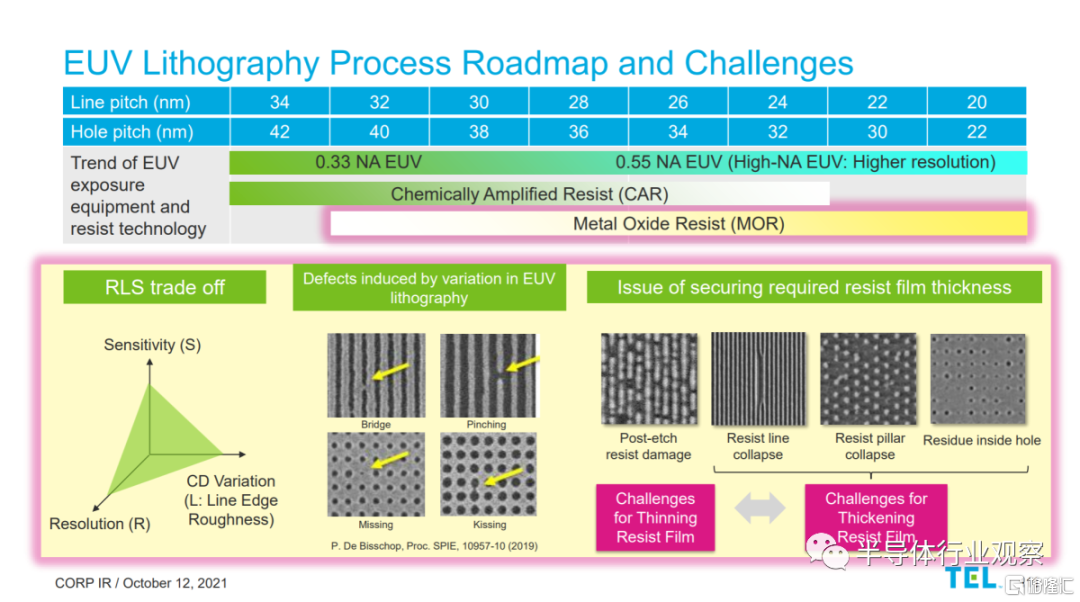

上面概述的光刻膠工藝已經出色地工作了幾十年,但它開始遇到重大問題。這與線邊緣粗糙度、靈敏度、分辨率和吞吐量有關。EUV 光刻使用相對於 DUV 而言極短波長的光來轟擊晶圓。較短波長的極紫外光的生成難度要大得多。

EUV 存在吞吐量問題。這個問題主要圍繞一個事實,即相對於DUV,EUV光刻機只有1/14劑量的光子打在晶圓上。因此,必須增加 EUV 中的劑量,這反過來又通過增加曝光時間來降低吞吐量。產能問題導致晶圓產量受到嚴重限制,成本增加。爲了最大化吞吐量,劑量被最小化,這會導致與特徵保真度相關的各種問題。

一種解決方案是使用更多的機器並從光源上入手,然而EUV光刻機機器極其昂貴,每臺約 1.5 億美元,而且ASML 的產量非常有限。至於增加光源功率,也相當非常困難,ASML 的功率增加路線圖遠不及 EUV 層在新節點上增加的速度。

除了更少的光子暴露在光刻膠上之外,EUV 光刻膠也吸收更少的光子。這主要因爲光刻膠溶液是光酸產生劑、粘合促進劑和穩定劑的極其精確的混合物。那就意味着如果在過程中出現差錯,會是一個代價高昂的錯誤。2019 年,臺積電的 Fab 14B 光刻膠出現問題,最終給他們帶來高達5.5 億美元的損失。使用 EUV 光刻膠,這種平衡行爲更加難以控制,因爲特定的混合物會導致吸收更少。對 EUV 的需求以及 1-2 次更少光子和更少吸收的需求相結合,爲經典光刻膠行業提供了一個成熟的機會。這就吸引廠商進入乾燥抗蝕劑(dry resist)市場。

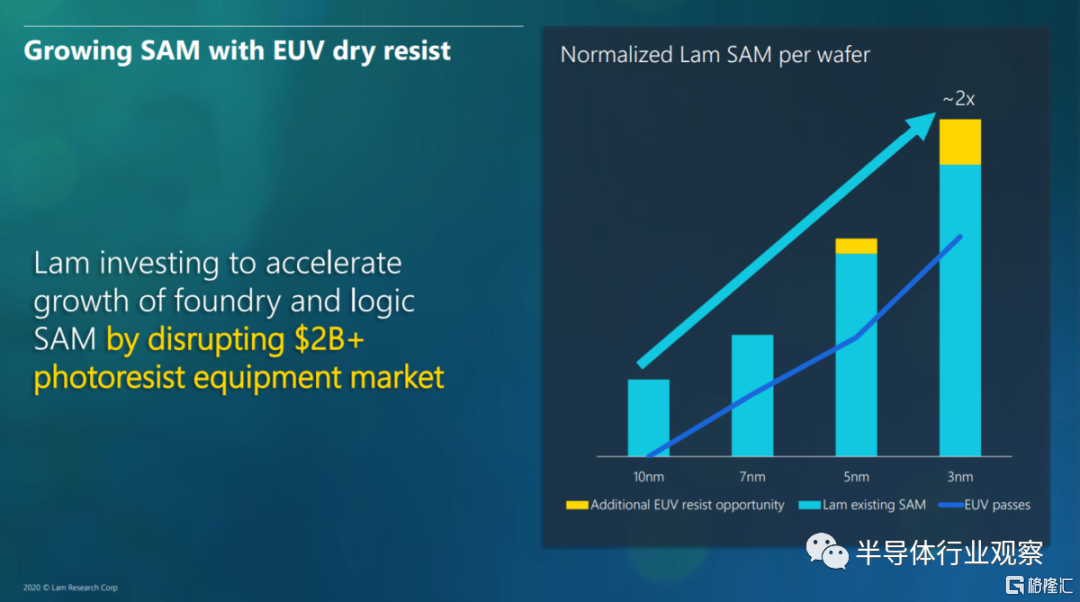

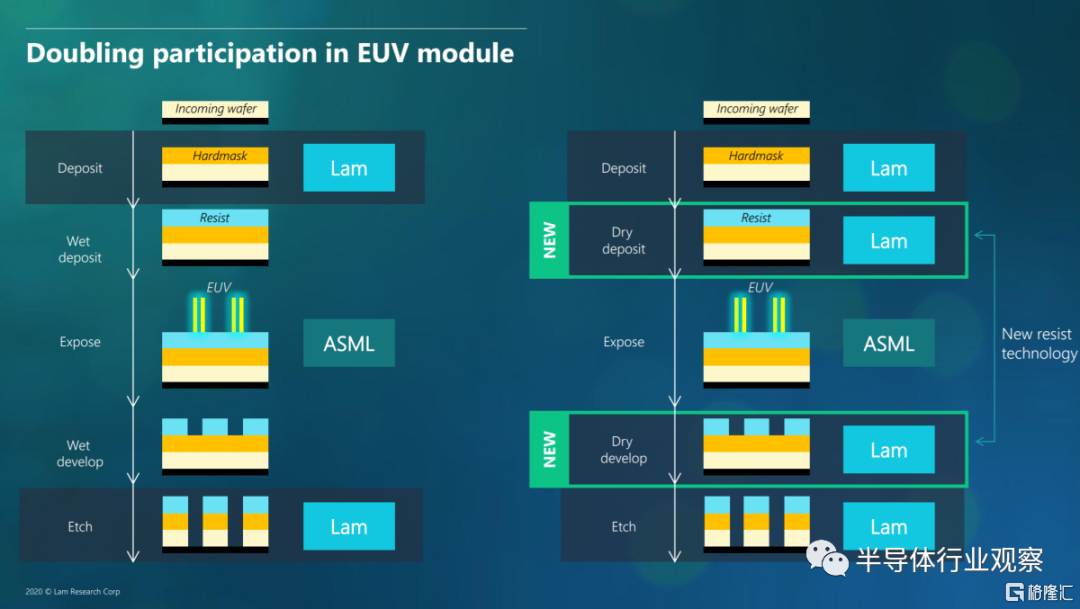

Lam Research 正試圖成爲當中的攪局者。他們將使用化學氣相沉積工藝在金屬光刻膠上分層,而不是使用旋塗機的溼式光刻膠(wet photoresist )技術。Lam Research聲稱乾式光刻膠技術(dryresist )與溼式光刻膠相比具有多項優勢。由於是一種密集沉積的金屬(metal),它不會與許多其他化學物質混合。這允許金屬光刻膠僅作爲吸收劑。回到吞吐量,這意味着每個晶圓通過和功率降低了 2 倍。每臺 EUV 工具吞吐量幾乎翻倍,這將大大降低成本。

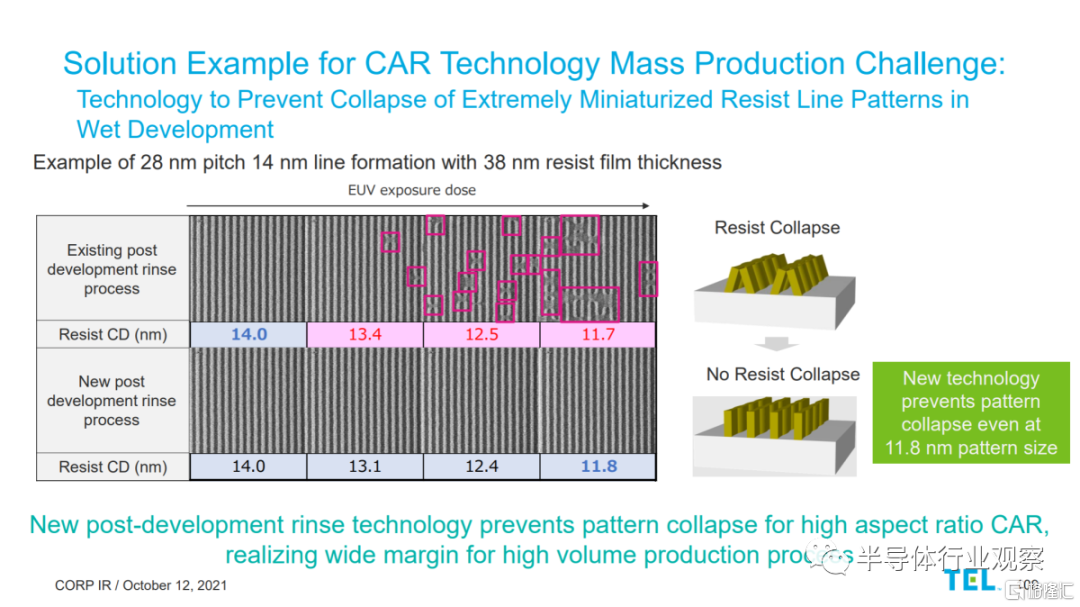

靈敏度並不是唯一的優勢。Lam 的乾式光刻膠也是採用幹法開發的。在溼顯影中,光刻膠用水或酸洗滌。當光刻膠由於毛細作用力溶解掉時,圖案化的線條和其他特徵可能會坍塌。隨着最小金屬間距 (MMP) 超過 28 納米,這越來越成爲一個問題。臺積電的 N5 和 N4 工藝節點的 MMP 分別爲 30nm 和 28nm,因此當前的出貨節點正好處於邊緣。

然而,東京電子仍有創新在進行中。雖然他們同意現有的開發沖洗工藝確實會導致超過 28nm 間距(14nm 臨界尺寸)的生產線塌陷,但他們發現了一種新的溶劑沖洗工藝,可以將其擴展到 ~24nm(12nm 臨界尺寸)。這將允許將溼抗蝕劑方法縮放到 24 納米。

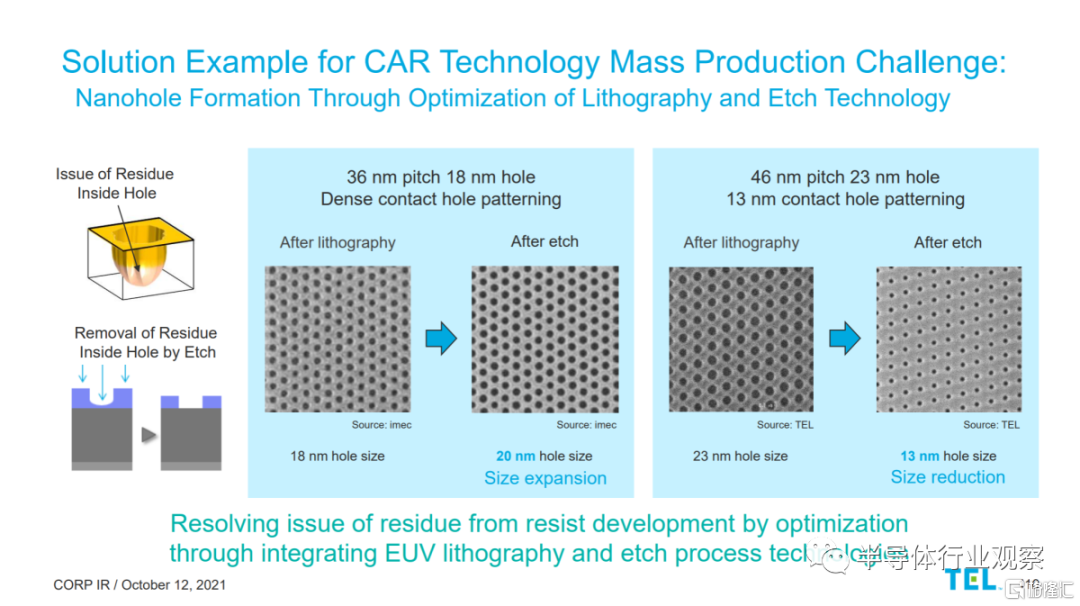

但並不是溼抗蝕劑的所有問題都解決了,因爲我們還是很難洗掉所有的光刻膠。如果所有的光刻膠沒有被洗掉,以後的步驟就會有問題。殘留的光刻膠在蝕刻時會導致孔洞,最終相互“親吻”。殘留物也可能導致這些孔完全丟失。

東京電子目前對此的解決方案是簡單地蝕刻殘留的光刻膠。雖然這是一個簡單的解決方案,但可能會出現複雜情況,因爲它會導致孔變大或傾斜。斜面效果不一定是負面的,但也不是在所有用例中都是最佳的。

Lam Research 聲稱他們的工藝可以實現 5nm 節點上使用的現有 32nm 間距,與現有的溼式光刻膠工藝相比,其方案具有更低的可變性和更好的寬容度。我們無法與 Lam Research 分享的硬性數字進行爭論。當晶圓廠追求特徵尺寸、性能和功耗時,幹法工藝總體上更好。由於顯示了當前部署的工具和流程與即將推出的工具和流程,因此 Lam Research 進行的比較可能被認爲是不誠實的。

與此同時,東京電子正在盡最大努力延長現有產品的壽命。他們的Clean Track Lithius Pro Z 與每臺 ASML EUV 機器一起使用。事實證明,它對於最初的 EUV 節點是可靠且高效的,但隨着行業超越單一圖案化 EUV,化學放大抗蝕劑 (CAR) 顯然已達到極限。在其他條件相同的情況下,乾式抗蝕劑將在前沿和最小特徵尺寸方面獲勝。

Lam Research 最初的目標是在 5nm IMEC 節點(代工廠爲 3nm)上使用。他們與 IMEC 和ASML 合作進一步開發這項技術。Lam 還與三星、英特爾、臺積電和 SKHynix 合作,將該技術用於邏輯節點和 DRAM 節點的商業化。這顯然很有希望。

面對洶涌襲來的新挑戰者,東京電子和光刻膠老牌企業並沒有坐以待斃, Inpria就是其中的代表。他們開發了一種新型光刻膠,金屬氧化物抗蝕劑 (MOR)。

Inpria 於 2007 年誕生於俄勒岡州立大學研究中心。此後,Inpria 獲得了來自三星、英特爾、應用材料、臺積電、SKHynix、JSR 和 TOK 的大量投資。

Inpria 的投資者是該行業的巨頭。它包括與 Lam Research 合作將乾式抗蝕劑商業化的所有 4 家公司。該名單還包括前面提到的 CAR 光刻膠的領導者JSR 和TOK 。JSR 在 2017 年和 2020 年參與了 Inpria 的幾輪融資,最近他們硬着頭皮以 5.14 億美元直接收購了該公司——對該公司的估值爲 7.42 億美元。對於一家以預收入爲基礎開發化學品的工業公司來說,這是一個令人印象深刻的估值。

很明顯,該公司擁有價值不菲的知識產權。JSR 管理往往非常保守,因此它充分說明瞭正在發生的中斷。光刻膠行業與 TokyoElectron 合作了數十年,而 JSR/Inpria 正在繼續這種緊密結合的夥伴關係。他們正在共同開發光刻膠、工藝和塗布機/顯影劑,以爲下一個即將實現商業化工藝節點做好準備。

MOR 仍然使用與當前光刻工藝類似的步驟。通過懸浮在溶液中,將其旋塗到硅片上。他們可以通過升級,從而可以在相同的Tokyo Electron Clean Track Lithius Pro Z上使用。這種升級不是資本密集型的,且可以使用 CAR 或 MOR 光刻膠。

MOR 仍然是溼的,這意味着某些問題仍將存在,即沉積的選擇性。晶圓上光刻膠的潛在不均勻沉積會導致曝光和烘烤工藝步驟出現問題。

Lam Research 乾式抗蝕劑技術的最大優勢之一是使用化學氣相沉積 (CVD) 工藝來沉積光刻膠,從而可以更精細地控制光刻膠的可變性和厚度。

衆所周知,獲得合適的厚度對於光刻膠來說非常重要。如果有極薄的層,則光刻工具具有更高的性能和吞吐量,因爲需要曝光的光刻膠更少。另一方面,蝕刻時會損壞薄抗蝕劑膜(負光致抗蝕劑)。厚的光刻膠層不僅會導致較低的吞吐量,還會導致圖案塌陷和顯影後殘留的光刻膠留在孔中。

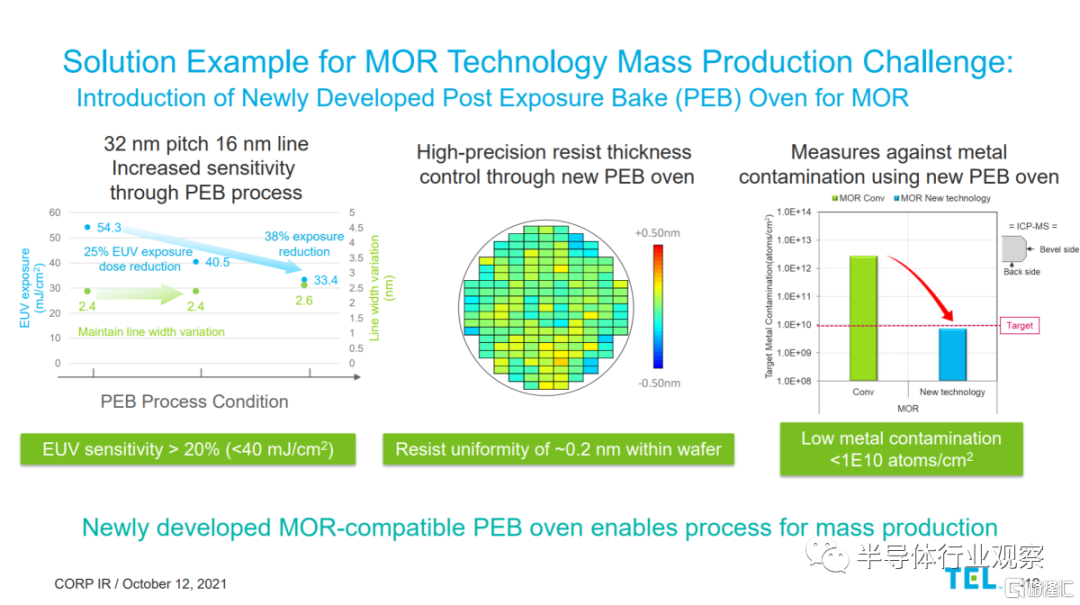

TokyoElectron 和 JSR 聲稱他們有一種新的金屬氧化物抗蝕劑曝光後烘烤工藝,這將有助於提高光刻膠的靈敏度。這意味着晶圓廠可以顯著降低 EUV 機器所需的劑量,從而提高產量。

TokyoElectron 聲稱用量減少了 38%,而 Lam Research 聲稱乾式抗蝕劑用量減少了 50%。Tokyo Electron 還聲稱新的曝光後烘烤可實現極其均勻的抗蝕劑厚度和低金屬污染。如果這些說法成立,那麼這可以延長溼光刻膠的使用壽命。

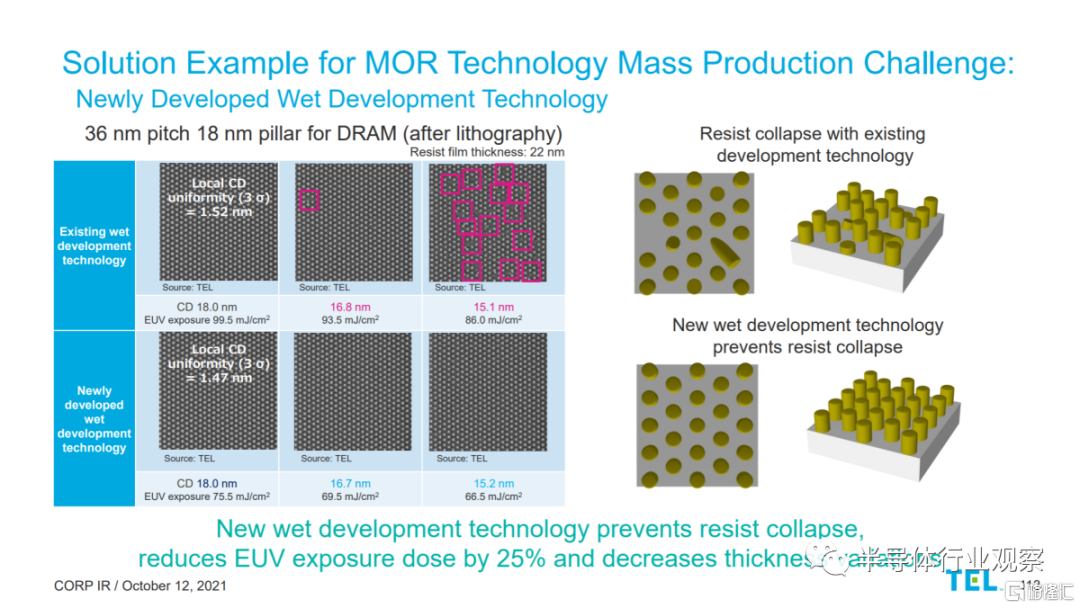

同樣,Tokyo Electron 和 JSR 擁有新的溼法開發工藝,可以抵抗支柱倒塌(pillar collapse )問題。36nm 支柱經常崩塌,這是 DRAM 中電容器縮放的最大挑戰之一。新的顯影工藝也適用於較低的 EUV 劑量,並減少了最終特徵的厚度變化。

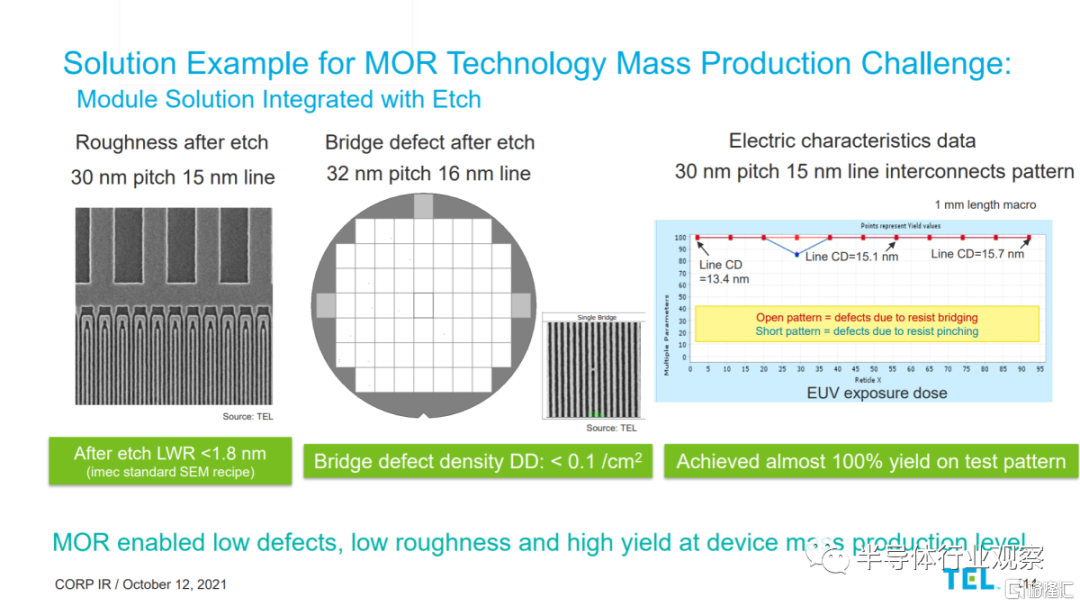

通過 MOR,Tokyo Electron 正在努力優化從塗層、烘烤、開發,並一直到蝕刻的整個工藝流程。他們聲稱他們已經實現了每平方釐米 0.1 個缺陷的缺陷密度。這聽起來很棒,但這種缺陷密度意味着每 300 毫米晶圓有 70.6 個缺陷。光刻工藝在前沿晶圓上進行了 70 多次,而 N3 工藝將對每個晶圓進行 20 多次EUV 浸漬。那就意味着這些缺陷確實開始堆積並破壞產量。MOR 仍有一些障礙需要克服。

優化流程的想法並不是一個全新的想法。工藝模塊優化是應用材料公司在其整個互連工藝流程和工具產品中已經做了很長時間的事情。由於東京電子在光刻膠塗布機/顯影劑中的主導地位,它使東京電子在蝕刻和清潔領域獲得了份額。Lam Research 同樣希望通過提供從硬掩模到光刻膠沉積和開發一直到蝕刻的技術來滲透光刻市場。多步驟工藝優化允許最終用戶芯片和工藝中的線邊緣粗糙度更小、更均勻、缺陷更少以及更高的可靠性。

幹法工藝顯著降低了化學品的使用。這尤其適用於旋轉抗蝕劑和顯影。光刻膠不需要懸浮在溶液中進行沉積,也不會像溼法工藝那樣產生廢料。顯影過程不需要用大量酸或超純水沖洗硅片以溶解硅片上的光刻膠。這反過來又將所需的電量減半。

EUV光刻膠爭奪,未來的輸贏還有待觀察,因爲兩種路線都都有好處,但毫無疑問,一場新的戰鬥已經打響。