本文來自格隆匯專欄:半導體行業觀察

在之前召開的IEDM年度會議上,總共進行了六次小組討論式的演講。其中,由IMEC Technology Solutions and Enablement的高級副總裁Myung‐Hee Na先生做的一個題爲《Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials》的演講最有意思。本篇開始將逐個回顧演講內容,由於演講內容有不充分的地方,筆者爲了讀者易於理解,適當地補充了演講內容。

需要說明的是,雖然這是一個說明未來CMOS邏輯技術的講座,但當中卻省略了數個基本的前提:

第一,以MOSFET(MOS晶體管)的結構爲前提。在28納米一一22納米的世代,芯片晶體管採用的是傳統的平面結構MOS晶體管技術,因此很難繼續微縮化。到了16/14納米及以後的技術節點時代,以FinFET爲代表的立體結構的MOS晶體管成爲了基礎前提。

第二,是支配CMOS邏輯性能的主要原因。之前,能否提升MOS晶體管性能(縮短延遲時間、增加ON電流)關係着CMOS邏輯的性能。但是,就大型、高速CMOS邏輯而言,無法忽視金屬排線引起的時間延誤(且越來越大)。對16/14納米世代以後的技術節點而言,縮短排線引起的時間延誤(或者不延長)對CMOS邏輯的性能提升極其重要。

2025年前的CMOS技術藍圖

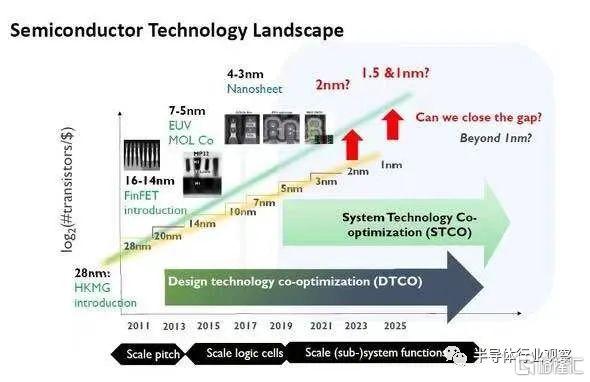

在演講之初,Myung‐Hee Na先生首先展示了CMOS邏輯生產技術的微縮化技術藍圖。時間軸(橫軸)範圍爲2011年一一2025年。縱軸爲用對數表示的單位生產成本(美元單元)下晶體管數量,以2爲底數。在2019年的7納米技術之前,幾乎都保持一定比率,從中也可以看出單位生產本下晶體管數量呈增長趨勢。

CMOS邏輯的微縮化技術節點、晶體管的生產成本(以美元爲單位下的晶體管數量、以2爲底數)推移。

以上技術藍圖詳細地說明瞭MOS晶體管技術的變遷。在28納米技術世代,平面型MOS晶體管導入了HKMG(High-K Metal Gate,高介電常數金屬閘極)技術。16/14納米技術節點下,晶體管走向3D化,成爲了FinFET。後來,FinFET持續了一段時間。

7納米技術到5納米技術器件,光刻技術發生了巨大的變化。不採用以往的ArF激光浸沒式光刻,而是導入了EUV(Extreme Ultraviolet,極紫外光刻)光刻技術。此外,將鈷(Co)金屬應用於MOL(middle of the line)的排線材料也開始被廠商引入。

4納米以後的技術則屬於未來。據預測,從4納米技術到3納米技術,晶體管將不再採用FinFET,而是納米結構的MOS晶體管。3納米以後的晶體管技術,即1.5納米技術、1.0納米技術後補將會在下一節進行說明。

就此技術藍圖而言,我們應該關注的是時間軸下面的內容。28納米技術到20納米技術之間的演進。在這個階段,支持微縮化(提高晶體管密度)的手段主要是利用光刻技術使排線和晶體管的節距(Pitch)縮小。但是,20納米以後,節距無法再縮短。於是,通過下調CMOS邏輯的基本單元(Standard Cell)的高度(按照最下層排線的數量來計算),與之前一樣提高了密度。但是,越來越難下調基本單元的高度。據預測,未來,會研發使副系統、線路邏輯實現微縮化的技術。

資料顯示,在28納米之前,通過縮短MOSFET柵極長度(Gate, Chanel 長度)和排線節距,邏輯的基本單元(Standard Cell)面積幾乎是每世代縮小一半,但是,22納米世代以後,柵極長度卻很難像以往一樣縮短了。短柵極效果使MOSFET的閾值電壓不均勻,最終導致無法縮短柵極長度。

因此,16/14納米世代之後開始使MOSFET的柵極3D化,在不縮短柵極長度的情況下,縮小MOSFET的尺寸(硅基板表面和平行方向的尺寸)。此處立體柵極的代表就是FinFET。通過縮小作爲柵極的Fin的節距,繼續實現微縮化。但是,與傳統的平面型MOSFET相比,尺寸縮小的比例變小了。這樣下去,就無法使基本單元的面積縮小一半。

於是,通過降低基本單元的高度(Cell Height),使基本單元的面積縮短至上一代的一半。基本單元的高度由與Fin保持同樣方向(水平方向)的最下層金屬排線(M0或者M1)的數量(Track數量)決定。比方說,10 Track(10T)的意思是一個基本單元上有10根金屬排線。如果在減少Track數量的同時,縮短節距,就可以大幅度降低基本單元的高度。在16/14納米到5納米的世代中,降低了基本單元的高度,這對縮小基本單元面積、即提高CMOS邏輯晶體管密度發揮了巨大作用。

但是,必須將排線的數量確保在某個範圍內。金屬排線由電源/接地線、信號線構成。都對CMOS邏輯的基本單元極其重要。

通過內埋電源/接地線,進一步減少排線的數量

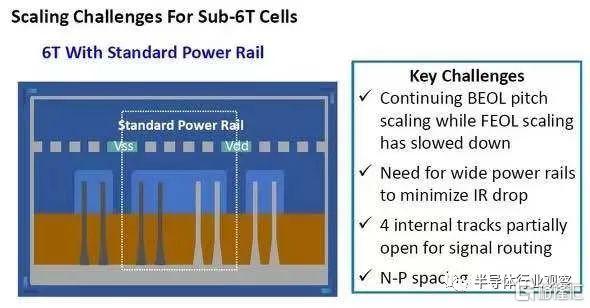

Myung‐Hee Na先生的演講中提到,很難將基本單元的Track數量從6T(Track)降至更低。下圖的基本單元是CMOS Inverter線路。在論述縮小基本單元的時候,一般會處理晶體管數量最小的理論柵極一一Inverter(理論反轉)。

下圖是imec的技術藍圖(相當於5納米節點的基本單元)。Fin數量如下,2個p 型FinFET 和n型FinFET。單元高度爲6T。如果想要進一步減少Track數量,就存在以下問題:難以使電源/接地線的寬度變得更細(原因是無法提高電阻)、難以縮小FinFET的尺寸、難以縮小p型FinFET和n型FinFET的距離(爲了確保元件分離)。

CMOS邏輯基本單元的斷面構造圖(FinFET的Fin和最下層金屬排線直接交叉方向的斷面圖)。單元的高度爲6Track(6T)。爲了進一步提高CMOS邏輯的密度,要想減少Track的數量,存在多個問題。

解決以上問題的有效辦法是將電源/接地線埋入基板,即BPR(Buried Power Rails)。利用BPR方法,可將Track數量減少至5T,此外,可以將信號排線數量保持爲4T。採用了BPR方法的5T單元,被imec定義爲3納米節點技術的後補。

將單元的高度下調至5T的CMOS邏輯的基本單元的斷面構造圖(FinFET的Fin和最下層的金屬排線直接相交方向的斷面圖)。將電源排線和接地排線埋入基板(BPR)。

由於可以提高BPR下的電源/接地線的縱橫比,因此,也容易降低電阻。但是,FinFET的Fin數量減少爲了一個,與6T 單元相比,晶體管(FinFET)的電流驅動能力(以柵極爲單位)會下降。晶體管的密度雖然得以提高,但很可能需要在防止性能下滑方面下功夫。

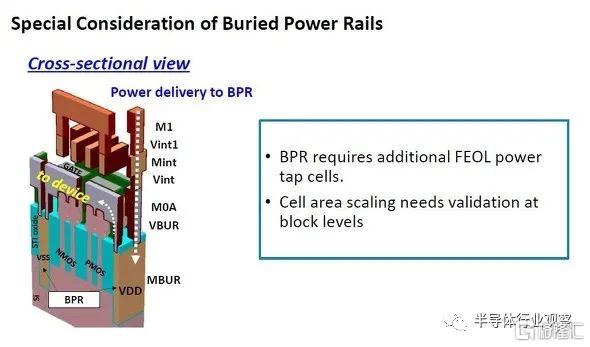

Myung‐Hee Na先生的演講中提到,通過採用BPR(Buried Power Rails,將電源/接地排線埋入基板的技術)技術和減少FinFET的Fin數量,實現了5T的基本單元。基本單元的斷面構造如上文所示。

導入了BPR之後,基本單元的構造將比之前更復雜,這是因爲需要從晶體管上面排列的電源/接地線網絡(PDN:Power Delivery Network)向BPR供給電源。具體而言,爲了將PDN的排線網絡和BPR結合,需要具有以下結構:在垂直方向形成連接導孔(Via)、電極層等的細長柱狀結構。在形成此種結構的工藝中,增加了晶體管的製造工藝(FEOL)。此外,也增加了基本單元的硅面積。

採用了BPR(BPR:Buried Power Rails,將電源/接地線埋入基板的技術)技術的CMOS邏輯基本單元的斷面結構。需要向BPR供給電源(白色箭頭部分)。

因此,不需要驗證BPR對基本單元造成的影響,而需要驗證對線路模塊的影響。實際上,對6T的線路模塊和5T的線路模塊分別進行了驗證。6T是FinFET的基本單元,5T是Nano-sheet(NS)FET和BPR的基本單元。

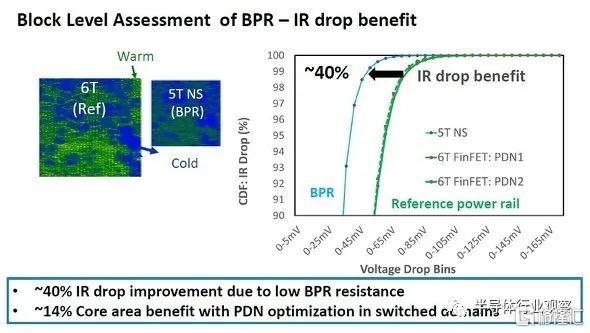

通過導入BPR,電源/接地排線引起的電壓下滑約爲40%,與之前相比下降幅度大幅度降低了。BPR情況下,即使排線較細,也可以保證高度,因此,很容易使排線的斷面積做的較大。即,可以降低電阻。BPR帶來的低電阻大大地緩解了電壓下降的問題(即有利於電源電壓的穩定)。

此外,通過優化供給電源的排線網絡(PDN),線路模組的硅面積大約減少了14%(排除以下:通過縮小晶體管、減少線路的Track數量,削減硅晶圓面積)。

利用線路模塊驗證了BPR的結果,左邊是比較了線路模塊的大小和溫度分佈。就採用了BPR的5T(Track)單元的線路模塊而言,溫度高的部分(Warm)在逐漸變小。右邊是比較了電壓下降(IR Drop)的累計分佈圖。在導入了BPR的5T單元的線路模塊中,電壓的下降幅度約減少了40%,與之前相比下降幅度大幅度降低了。

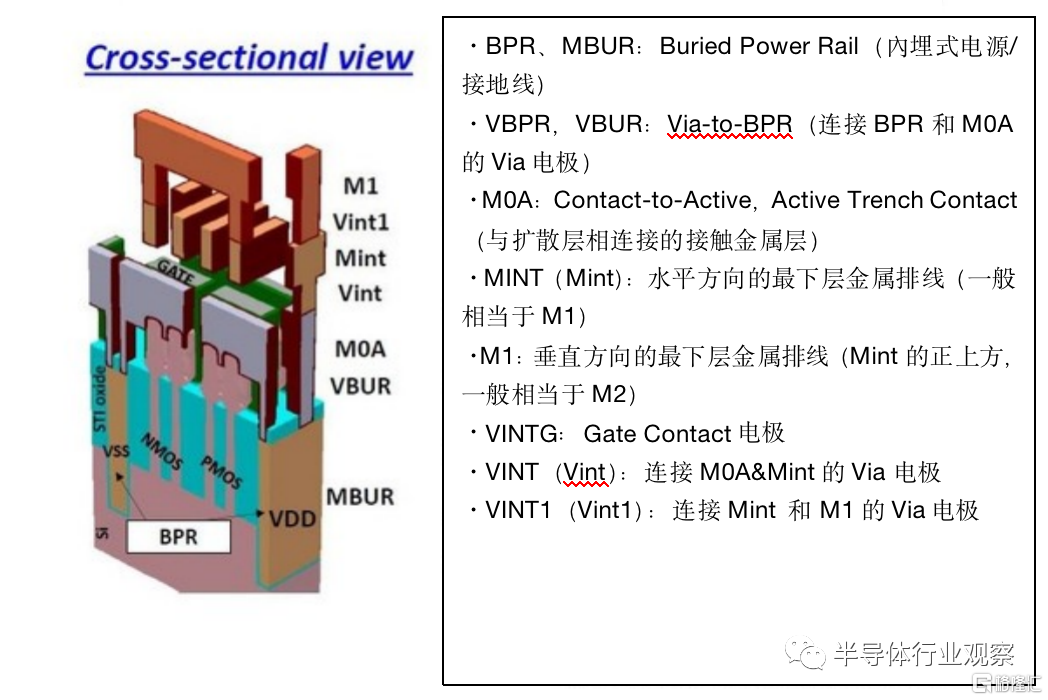

我們必須再強調一下,BPR是有希望的後補選項,通過導入BPR,能夠有效控制電源電壓的下降。此次,在說明BPR複雜結構的縮略語的同時,介紹一些金屬材料的備選項。

BPR結構的CMOS基本單元具有非常複雜的構造。

導入了埋入式電源/接地線(BPR)的CMOS基本單元的結構和主要的縮略語,此圖引用自小組演講《Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials》的幻燈片,右圖的縮略語是筆者從imec的學術論文中摘選的。

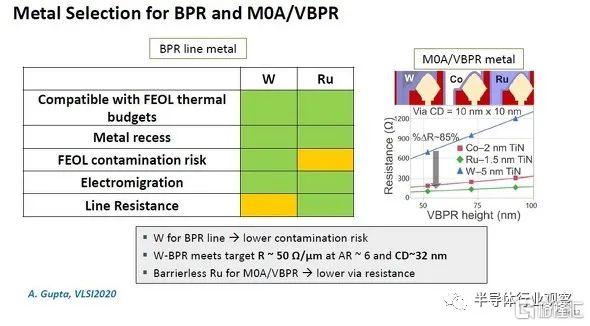

一般情況下,金屬排線使用銅(Cu)作爲材料。但是,內埋式電源/接地線(BPR)很難使用銅(Cu)。這是因爲需要一道蝕刻排線層的工藝。於是,在BPR結構下,鎢(W)、釕(Ru)、鈷(Co)等金屬材料是備選項。

對於內埋式電源/接地線(BPR)的排線結構而言,比較各種金屬。左邊是比較了BPR材料特性,右邊是M0A、BPR的材料、BPR的高度(深度)情況下的不同電阻。

作爲BPR材料,比較了鎢(W)、釕(Ru),單位長度下,Ru的電阻較低,但是,釕(Ru)有污染(Contamination)的風險,另一方面,就VBPR和M0A而言,釕(Ru)和鈷(Co)的電阻更低。與鎢相比,作爲阻擋金屬(Barrier Metal,氮化鈦TiN,電阻較高),釕和鈷可以將厚度做的更薄。

BPR的構造(左)和BPR的電阻(中間)、VBPR的電阻(右)。

可以看出,可將鎢用做BPR的材料,釕用作VBPR和M0A的材料。鎢可以確保通過提高縱橫比,來降低電阻。釕具有使阻擋金屬變薄的特性。此外,釕也可用於不需要阻擋金屬的VBPR,有望用於2納米。

3納米後,電源電壓是一大課題

就3納米世代以後的CMOS邏輯而言,縮小基本單元的有效方法是將電源/接地排線埋入基板內的BPR技術,上文已經論述。在電源系統中,基本單元的電源/接地排線位於最末端。其上端爲有電源供給網絡(PDN:Power Delivery Network),是用於給大量的基本單元供給電源的。

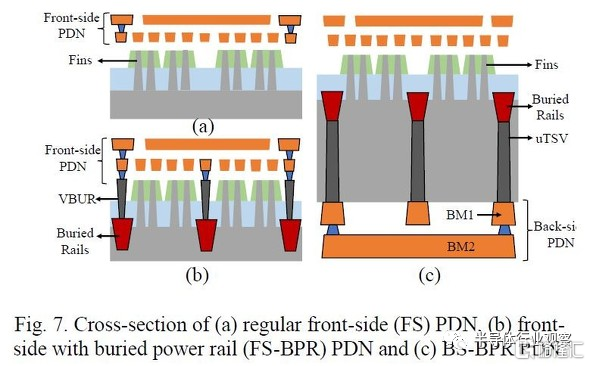

通常,PDN分割多層金屬排線的一部分。通常,PDN在硅芯片(Silicon Die)的表面(FS:Front Side),這種排線方式被稱爲“FS-PDN”。

在導入BPR之前,包含各個基本單元的電源/接地排線的PDN位於硅芯片的表面。爲了縮小基本單元,導入了內埋了基本單元的電源/接地排線的BPR。於是,就需要一個從FS-PDN向BPR垂直供給電源的電極排線(VBPR:Via to BPR)。

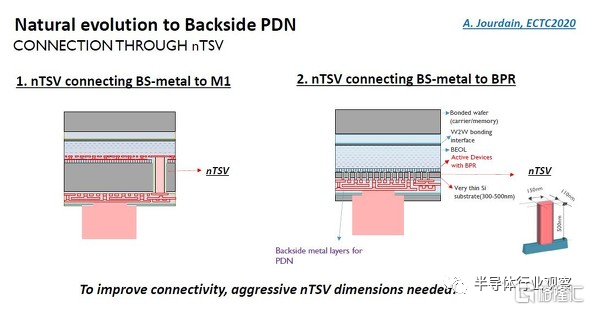

從削減硅面積的觀點來看,VBPR的存在是不被希望看到的。於是,通過將PDN配置於硅芯片的背面,來削減VBPR。這被稱爲“BS-PDN”。BS-PDN”和BPR之間由細微的TSV(硅通孔)連接。

電源供給排線網(PDN:Power Delivery Network)的分佈圖,左上角(a)爲傳統的佈局。所有的電源排線都包含在多層金屬排線層內。左下角(b)爲將BPR(內埋式電源/接地排線)導入到基本單元的佈局。右邊(c),在導入BPR的同時,將PDN配置於硅芯片的背面。

製造BPR和背面的電源供給網(PDN)的工藝極其複雜。利用細微的TSV(uTSV或者nTSV)將BPR和BS-PDN連接的同時,還需要一道在硅晶圓背面形成金屬排線的工藝。

利用了細微的TSV(nano-TSV,nTSV)的背面排線和表面排線的連接事例。左邊爲一般的連接結構。右邊爲用nTSV將背面排線(電源供給排線網,PDN)和內埋式電源線(BPR)連接的結構。

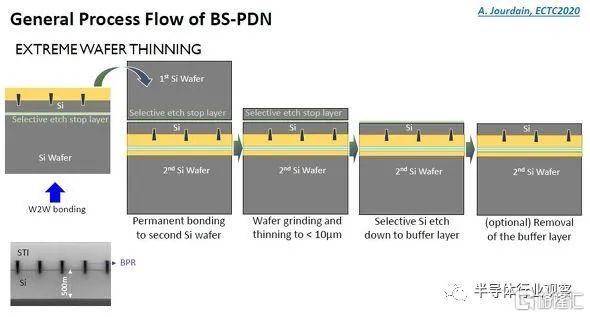

比方說,將具有了BPR的硅晶圓(1st wafer)與其他硅晶圓(2nd wafer)貼合,然後研磨1st硅晶圓,在經過蝕刻,使厚度爲10um左右。

在硅芯片背面製造電源供給排線網(PDN)的工藝(前半部分)。

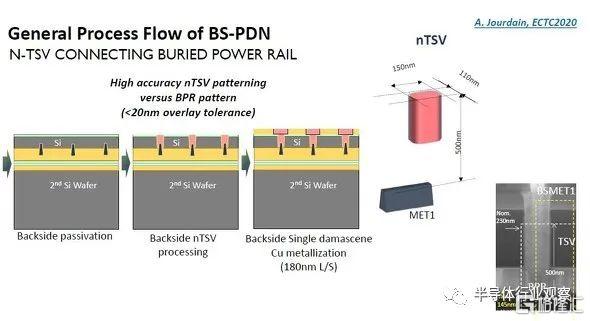

然後,形成連接了BPR的nTSV。nTSV的內埋金屬是銅(Cu)。形成nTSV後,通過單邊鑲嵌工藝(Single Damascene),生產銅排線層的BS-PDN。

在背面生產電源供給排線網(BS-PDN)的工藝(前半部分)。

此外,還評價了CMOS邏輯的基本單元(Standard Cell)的BPR & BS-PDN的效果。以6T(Track)的基本單元(沒有BPR, FC-PDN)爲基準的情況下,導入了BPR的5T(Track)的基本單元(FS-PDN)的線路模塊的面積減少了19%,電源電壓下降值從45mV減少爲35mV。此處,追加BS-PDN的話,線路模塊的面積雖然不變化,電源電壓下降值更低,爲25mV。與6T單元相比,可將電源電壓的變化控制爲45%。

BPR和BS-PDN的效果。左邊是線路模組(Core)的面積和電源電壓下降的關係。右邊是線路模組的溫度分佈(反應IR Drop的大小)。

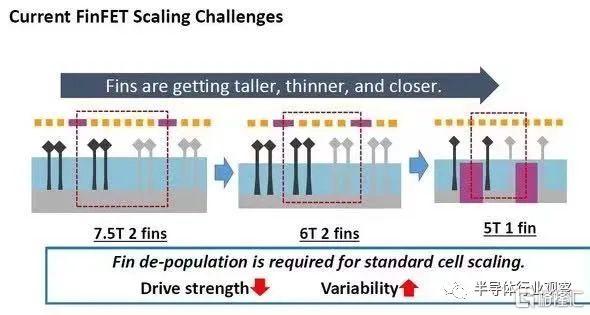

3nm後,FinFET到達極限

正如我們之前說明的一樣,就以FinFET爲晶體管的CMOS邏輯而言,在縮小Fin的節距的同時,將Fin擡高,通過減少與Fin平行的的最下層的金屬排線的數量(Track數量),來縮小基本單元(Standard Cell)。比方說,就7.5Track的基本單元而言,通過Fin的2個p型FinFER和n型FinFET,構成CMOS Inverter。就下一代而言,在保持Fin的數量的同時,通過將Track數減少爲6個,來縮小基本單元的面積。

此外,就下一代而言,預計會將Track數量減少爲5個的同時,Fin的數量減少爲一個,從而縮小基本單元的面積。減少Fin的數量是爲了保持p型FinFET和n型FinFET之間的距離(是能夠分割元件的距離)。

此處存在的問題是每一代產品對FinFET的規格要求都在變化,同時,在變得越來越嚴格。減少Fin的數量會導致FinFET的電流驅動能力變弱。爲不使電流驅動變弱,必須要提高單個FinFET的的電流驅動能力。此外,如果使Fin做得更薄、減少節距,加工尺寸、異物濃度等帶來的問題影響將會更大。

採用了FinFET的CMOS基本單元(Standard Cell)的微縮化和其存在的問題。

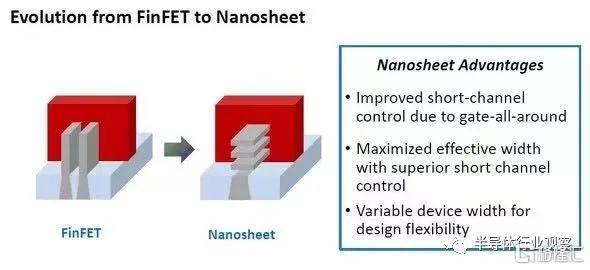

可以想到的解決方案是將FinFET的Fin由垂直改爲平放的Chanel 結構(Nano結構)晶體管。被稱爲“Nano-sheet FET”、“Nano-ribbon FET”。Fin的結構如下:Fin的側面有2個柵極(Gate)、頂點有一個柵極(Gate),合計爲三個(Tri-gate);而Nano-sheet結構的優勢如下:上面兩個柵極、下面兩個柵極,合計四個(Gate-All-Around)。在控制短Chanel效果的同時,由於Chanel的寬度變寬,所以電流驅動能力得以提高。

此外,與Fin結構相比,Nano-sheet結構的晶體管的性能差異更小,且由一片薄薄的Sheet的厚度決定晶體管的電流驅動能力。在半導體生產工藝中,厚度(垂直方向的尺寸)由原子層單位控制。Fin的厚度(橫向尺寸)是通過光刻技術加工的,加工尺寸的偏差無法做到某個值(比原子層更長的距離)以下。

從FinFET到Nano-sheet的轉換和Nano-sheet的優勢。

另一個重要的方面是佈局(Layout)自由度的增加。就FinFET而言,Fin的數量由橫向尺寸決定。由於Fin的數量是自然數,因此橫向的尺寸是離散決定的。就Nano-sheet FET而言,由於是垂直堆疊sheet,因此,可以連續地改變橫向的尺寸。

爲了通過FinFET來縮小CMOS的基本單元(Standard Cell),需要採用以下方法:減小Fin的節距、減少Fin的數量、使Fin做得更薄、擡高Fin。於是,FinFET的每個Fin的電流驅動能力雖然得以提高,卻又需要縮小每個Fin之間的差異。這個問題和微縮化一樣,很難處理。

此處考慮到的方案是將FinFET橫向放置的Chanel結構(Nano-sheet 結構)晶體管。

Nano-sheet 結構的晶體管(或者稱爲“Nano-sheet Transistor”)或者“NSH Transistor”的優勢是:電流驅動能力較高,偏差小。但是,imec似乎對於Nano-sheet 結構的開發並不是十分積極。主要理由如下:對於晶體管之間的分離元件而言,Nano-sheet 結構需要與FinFET一樣的距離。

從FinFET到Nano-sheet構造、Fork-sheet構造的變化。

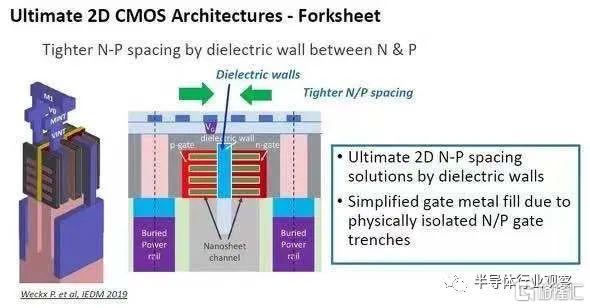

Imec主推的是被稱爲“Fork-sheet構造”的Chanel構造的晶體管(也被稱爲“Fork-sheet Transistor”或者“FSH Transistor”)。通過以Nano-sheet構造爲基礎進行重要的改良後,晶體管間的距離似乎縮小了。對於2納米以後的世代而言,Fork-sheet構造是晶體管技術的有力備選項。

就Fork-sheet構造而言,絕緣膜的薄壁位於中間,p型Nano-sheet和n型Nano-sheet成對。柵極金屬的斷面結構與作爲餐具的叉子形狀類似,因此被稱爲“Fork-sheet”。

就Fork-sheet構造而言,相鄰的Chanel和柵極金屬在物理上是分離的。因此,相鄰的晶體管之間的距離已經縮小至極限。即,CMOS邏輯的基本單元可以縮小。

Fork-sheet構造,嵌入將p型和n型的晶體管的模式圖。

此外,與Nano-sheet相比,Fork-sheet構造具有寄生容量較小的優勢。在消耗同樣電力的情況下,與Nano-sheet構造相比,Fork-sheet構造的晶體管可以更高速地工作。反過來說,在同樣工作頻率的情況下,Fork-sheet構造比Nano-sheet耗費的電力更少。從imec在國際學會IEDM 2019上發佈的論文(論文編號:36.5)來看,用CMOS Inverter的15段 Ring振盪器比較後發現,Fork-sheet構造的工作頻率(以同樣的功耗來比較)提高了10%,功耗(以同樣的工作頻率來比較)減少了24%。

Fork-sheet晶體管成爲候補的理由

我們已經在上文敘述過使基本單元微縮化的有效辦法,即減少與Chanel方向(細長的Active區域)平行的最下層的金屬排線數量(Track數量,T)。通過減少Track數量,縮短基本單元的高度(CH: Cell Height)。但是,這種辦法在6T的時候達到極限,據預測,可以採用將電源/接地線埋入基板內的BPR(Buried Power Rail)方法實現5T。

CMOS邏輯基本單元的架構和各部分的尺寸。左邊淡藍色爲最下層的金屬排線,垂直延伸的紅色部分爲柵極金屬、水平延伸的綠色部分爲Active區域。

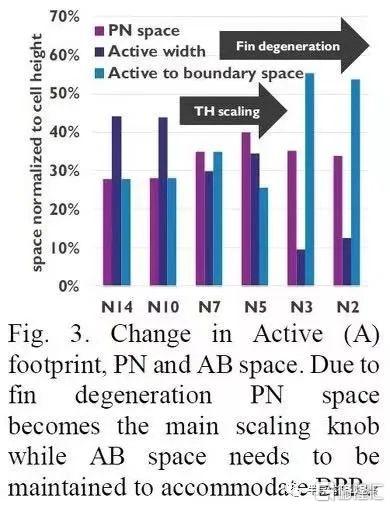

就此處規定基本單元(CMOS Inverter)的高度的定義而言,如下,從Active區域到基本單元區域的距離爲“AB(Active to Boundary)”、Active區域的高度爲“A(Active)”、分割p型晶體管和n型晶體管的距離爲“PN(p to n)”。

接下來,按照CMOS邏輯技術的節點,來逐個討論基本單元各部分高度(CH)的尺寸。在14納米(N14)、10納米(N10),40%(甚至更多)的CH由“A”佔據,“PN”、“AB”分別各佔三成(甚至更低)。在7納米(N7),“A”的比例減少至三成,“PN”、“AB”分別增加至三成多。早接下來的5納米(N5),“PN”的比例進一步增加,增至四成,另一方面,“AB”的佔比減少至2.5成,而“A”的佔比反而增加至3.5成。

各部分在基本單元高度(CH)中的佔比和技術節點(N)的推移。

3納米以後,由於導入了BPR技術,“AB”的比例達到五成以上,爲最大值。這一比例沒有什麼變化。“A”的比例大幅度減少至一成,另一方面,“PN”佔比爲3.5成左右,也比較高。N5以後,“PN”雖然變得較短,但是卻是微縮化的關鍵。

從以上可以看出,能夠縮短“PN”的“Fork-sheet構造”比“Nano-sheet構造”更有優勢。這也是imec的觀點。

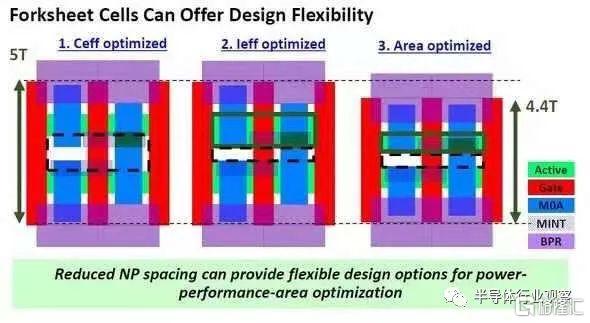

我們也應該認識到,Fork-sheet構造具有單元佈局自由的優勢。這是因爲可以控制“PN”、“A”。在演講中,提到了使寄生容量最小化的佈局、使電流驅動能力最大化的佈局、使單元面積最小化的佈局。

就將寄生容量最小化的佈局而言,Active區域不是很寬、且適當地確保了晶體管間的距離。就使電流驅動能力最大化的佈局而言,在擴大Active區域的同時,縮小了晶體管間的距離。就使單元面積最小化的佈局而言,Active區域較細、縮小了晶體管間的距離。單元的高度控制爲4.4T。

Fork-sheet構造,優化了基本單元佈局的事例。左邊爲寄生容量最小的佈局、中間爲提高了電流驅動能力的佈局、右邊爲單元面積最小化的佈局。即圖中的“M0A”爲“Contact-to-Active, Active Trench Contact(與Active層相連接的接觸金屬層)”、“MINT”爲“水平放下的最下層金屬排線(一般相當於M1)”、“BPR”爲“Buried Power Rail(埋入式電源/接地線)”。

接下來,我們在敘述Fork-sheet構造的CMOS邏輯的生產工藝的同時,也會公佈用電子顯微鏡和熒光X線觀察的晶體管的斷面圖(試作品)的圖像。

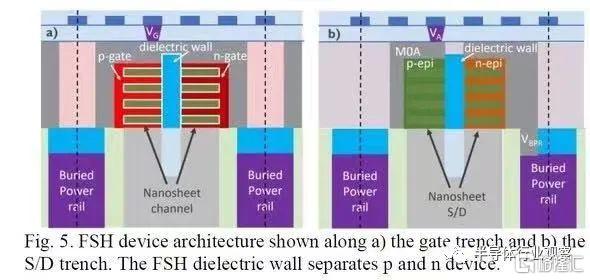

構成Fork-sheet(FSH)構造的CMOS邏輯的一對晶體管的斷面構造圖。左邊的構造圖(a)是在柵極電極處的斷面。這對晶體管的左邊是p型,右邊是n型。右邊的構造圖(b)是Active區域的斷面(Source/Drain區域)。用絕緣膜壁用電和物理特性使晶體管分開。

這一對Fork-sheet構造的晶體管(一對p型和n型)具有非常複雜的結構,乍一看,很難想象是以何種工藝製成的。

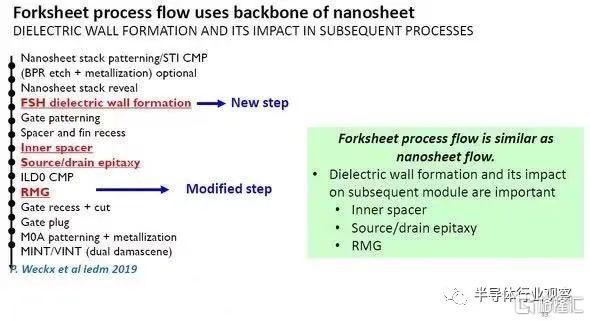

以Nano-sheet的生產工藝爲基礎,針對Fork-sheet,追加和變更了一部分。

根據Myung‐Hee Na先生的演講,Fork-sheet構造的生產工藝是Nano-sheet構造生產工藝的基礎。不僅在Fork-sheet構造中追加了特殊的工藝,還針對Fork-sheet進行了部分工程變更。

最大的差別是增加了形成絕緣膜壁的工藝(Step)。此外,將形成內部Spacer的工藝和Active(Source、Drain)層的外延生產工藝、形成RMG(Replacement Metal Gate)的工藝全部改爲了針對Fork-sheet構造。其他工藝與Nano-sheet構造的晶體管工藝基本相同。

Fork-sheet構造晶體管的生產工藝流程

再稍微具體一些說明,首先加工Nano-sheet壓層形狀的模板,形成淺槽分離層(STI:Shallow Trench Isolation),通過CMP(Chemical Mechanical Polishing)達到平坦效果。接下來,實施埋入式電源/接地排線(BPR: Buried Power Rail)的蝕刻和成膜工藝(此處的BPR工藝是選擇性的)。然後,使Nano-sheet的壓層結構曝光,形成用於Fork-sheet的垂直絕緣膜(絕緣膜壁)。

然後,進行以下工藝:加工柵極的線路(Pattern)、形成Spacer、Fin的Recess、內部Spacer、Source/Drain的外延生長、形成層間絕緣膜(ILD)和CMP、形成RMG、柵極的Recess和Cut、形成柵極的Plug、Metallization。

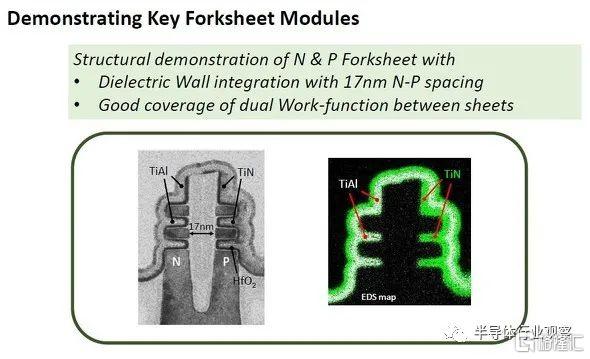

在演講中,Myung‐Hee Na還展示了用電子顯微鏡和熒光X線分光設備觀測的Fork-sheet構造的試作品(是按照以上工藝進行試做的)的圖像。由絕緣膜壁分割的一對晶體管的距離爲17納米。可以看出,柵極絕緣膜和柵極金屬膜很整齊地融入在壓層薄片(Sheet)裏。

試做的Fork-sheet構造的斷面圖像,左邊爲用透射電子顯微鏡觀察的圖像。右側爲用能量分散型熒光X線分光設備(EDS:Energy Dispersive X-ray Spectrometer)拍攝的Mapping 圖像。

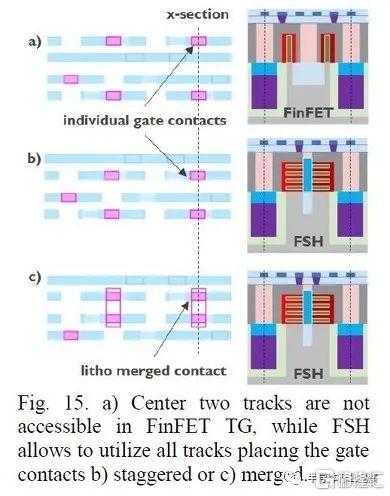

就理論線路單元而言,與FinFET相比,Fork-sheet構造的CMOS邏輯的佈局(Layout)自由度更高。具體而言,FinFET的CMOS Inverter的連接Track(水平方向的最下層的金屬排線)和柵極的連接位置是受限的。無法使中間的2個Track連接。但是,如果是Fork-sheet構造,可以使中間的2個Track連接。

CMOS基本單元(Inverter)的佈局(Layout)和柵極連接(Gate Connect)的佈局(Layout)。上部(a)的晶體管是FinFET。水平方向有4個Track,但中間的2個Track無法做到柵極連接。中間的(b)和下面的(c)的晶體管是Fork-sheet構造。所有的Track都可以與柵極連接。

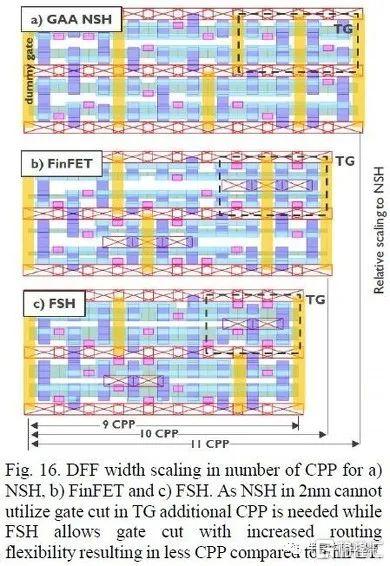

接下來,比較一下D類Flip Flop(D-FF)的理論線路單元。同樣高度的單元,Contact Gate Pitch(CPP 或者“CGP”)數量會不同。Nano-sheet(NSH)構造爲11Pitch,FinFET爲10 Pitch,Fork-sheet(FSH)構造爲9 Pitch。與NSH構造相比,FSH構造的D-FF的單元面積小了20%左右。

D類Flip Flop(D-FF)的單元佈局。自上而下:Nano-sheet(GAA NSH)構造(a)、FinFET(b)、Fork-sheet構造(c)。

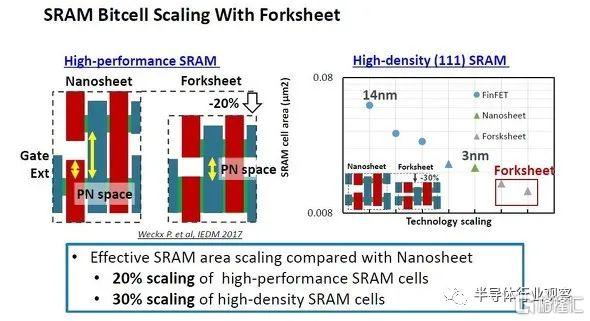

我們還分別比較了在高性能佈局和高密度佈局下的Nano-sheet構造和Fork-sheet構造的SRAM。就高性能的SRAM單元而言,Fork-sheet構造可以縮短p Chanel和n Chanel的距離(PN),因此,單元面積可以減少約兩成左右。如果是高密度的SRAM單元,單元面積可以減少約三成。

比較了在Nano-sheet構造和Fork-sheet構造下的SRAM的單元面積。左邊爲高性能的SRAM的單元。右邊爲高密度的SRAM的單元。

2nm後的晶體管選擇

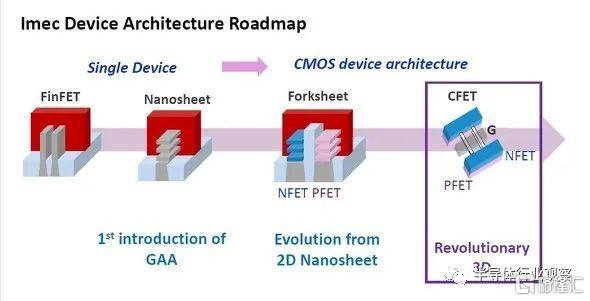

FinFET的“下一代的下一代”技術指的是Nano-sheet構造和Fork-sheet構造的下一代。Nano-sheet構造和Fork-sheet構造被認定爲屬於同一時代的技術(FinFET的下一代)。雖然Nano-sheet構造和Fork-sheet構造比較類似,但是晶體管構造有很大的不同。Nano-sheet構造是晶體管的單獨構造,Fork-sheet構造是以CMOS 邏輯爲前提的。

可以說,將兩個晶體管進行高密度融合並生產出來,纔是Fork-sheet構造。

imec所考慮的晶體管的技術藍圖。從FinFET到Nano-sheet、Fork-sheet的各代技術。平面(2D)構造的晶體管已經達到極限,因此新一代的3D(壓層)構造的CFET(Complementary FET)是有希望的備選項。

FinFET的“下一代的下一代”的晶體管的前提與Fork-sheet構造相同一樣、即CMOS邏輯。Fork-sheet構造的特點爲“PN距離(爲分離p Chanel 和n Chanel的晶體管的距離)較短”,且這一特點還在被改善。

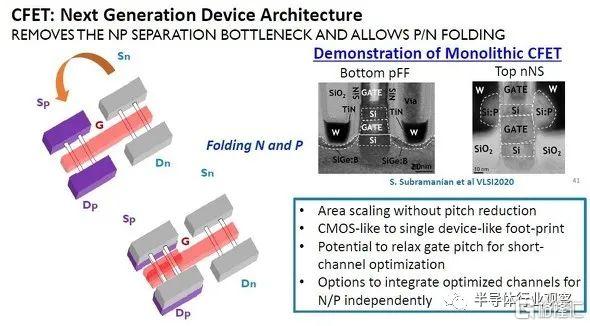

具體而言,在p Chanel晶體管的FET上重合n Chanel的FET。硅面積就減少爲一個晶體管的分量,理論上密度會提高。此外,由於“PN 距離”的進一步縮短,理論上CMOS 邏輯的工作速度會提高。這種晶體管的結構被稱爲“互補型FET(C FET,C=Complementary)”。

CFET的想法比較簡單。由平面型的p Chanel MOSFET和n Chanel MOSFET構成的CMOS Inverter共同擁有細長的柵極電極。以柵極電極的中線爲中心線,摺疊兩個晶體管。在p Chanel FET的上面重合n Chanel FET的3D壓層結構的晶體管會是一對(兩個)。

之所以把p Chanel FET放在下面是因爲標準的生產工藝順序,即首先生產p Chanel,然後生產n Chanel。理論上來講,把n Chanel FET放在下面也可以製成CFET。

“互補型FET(C FET,C=Complementary)”,S爲Source、D爲Drain、G爲Gate

如果要再次描述一下CFET的特點的話,首先一點就是縮小CMOS基板單元。與以往的晶體管線路相比,硅晶圓面積減少了約一半。可以用接近一個晶體管的硅面積製作由兩個晶體管構成的CMOS元件,此外,p Chanel的材料和n Chanel的材料是可以分別選擇的。

“互補型FET(C FET,C=Complementary)”的特點、用電子顯微鏡觀察的試做的晶體管的斷面結構圖像。

在2納米世代技術以後,CFET會成爲CMOS 邏輯的有力備選項。在1.5納米世代、1.0納米世代,CFET將會是必選項。

就CMOS基本單元(Inverter)的佈局(Layout)而言,是多個Chanel處於水平方向。與Chanel平行佈局的最下層的金屬排線數量(Track:T)決定着單元的高度(CH)。金屬排線數量的減少直接關係着單元高度的降低。

最初,是通過CMOS基本單元(把晶體管技術當做FinFET)來減少Track 數量(T)的。7.5T和6T都是在FinFET的情況下減少了Track數量。但是,5T情況下就很難用傳統技術來降低單元的高度了。首先考慮到的是保持FinFET不變,然後採用BPR(Buried Power Rail,將金屬排線的電源/接地線埋入基板)方法。實際效果如下:減少了兩根金屬排線。

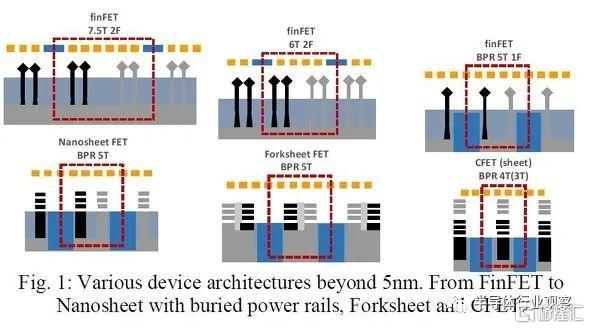

5納米世代以後的晶體管技術(斷面構造圖)的選項。上面三個是FinFET,下面自左開始爲Nano-sheet FET、Fork-sheet FET、 CFET。

通過融合BPR和FinFET,5T Fin的數量是每個晶體管一張,但是晶體管的性能有可能會下降。於是,通過將晶體管從FinFET改爲Nano-sheet構造和Fork-sheet構造,與FinFET相比,晶體管的性能得以提升,同時,晶體管的密度也易於提高了。高度爲5T的CMOS的基本單元有Fin FET、Nano-sheet、Fork-sheet三個選項,且是混合存在的。

但是,就4T以後的Low Profile而言,如果採用將p Chanel FET 和n Chanel FET放在硅表面的CMOS元件的話,比較困難。引進將p Chanel FET 和n Chanel FET垂直堆疊在硅表面的CFET(Complementary FET),是業界所希望的。

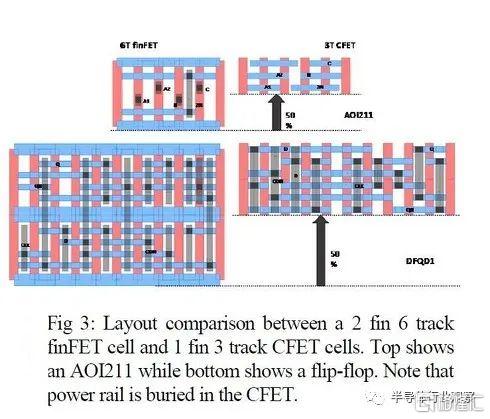

imec認爲,可以通過導入CFET,使CMOS的基本單元的高度降低至4T或者3T。比方說,可以將與6T的2Fin型FinFET具有同樣功能的理論單元(AOI,AND-OR-INVERT )211 Cell和DFQD1 Cell( Flip Flop)佈局爲3T(是CFET的一半)。

FinFET 的理論線路單元(6T)、CFET的理論線路單元(3T)。運用CFET,可以將理論線路單元的高度縮短爲FinFET的一半。

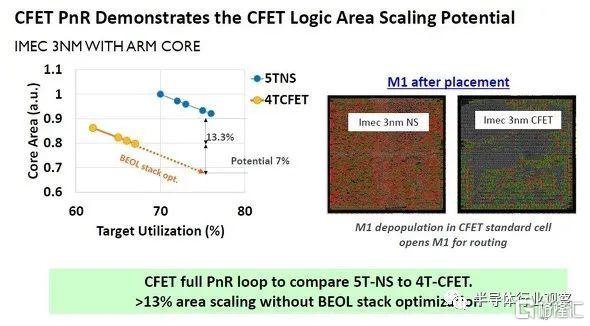

此外,就拿3納米世代的Arm 處理器來講,與5T Nano-sheet構造相比,4T的CFET的核(Core)面積會減少13.3%。此外,採用CFET,可以全部使最下層的金屬排線(M0)相互連接(Routing),因此,可以將與M0直接相交的第一層金屬排線(M1)分配爲輸入、輸出的Pin或者相互連接等。如果靈活運用這一優勢,優化金屬排線工序(BEOL),預計可以進一步將核(Core)的面積減少7%。

總而言之,在3nm之後,芯片產業將迎來巨大變革!

Arm 處理器核的硅面積比較值(相對值)。與5T的Nano-sheet構造相比,4T的CFET的核(Core)的面積減少了13%(左邊)。此外,CFET情況下,第一層金屬排線(M1)的Routing還有餘地(右邊),因此通過優化金屬排線工藝(BEOL),可以進一步減少核(Core)的面積。