本文來自格隆匯專欄:半導體行業觀察;作者:李晨光

在經歷了前兩年的芯片短缺之後,半導體市場進入了長期的下行週期。

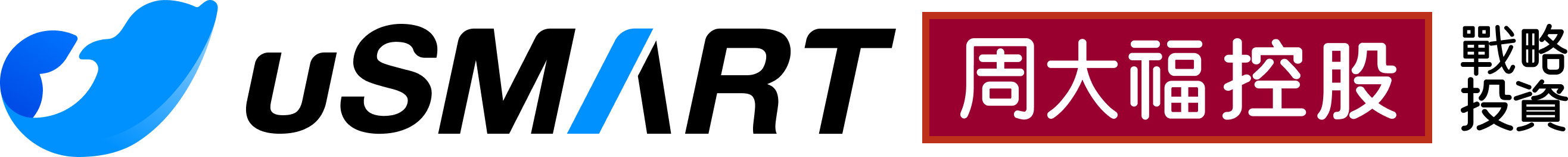

其中,存儲市場無疑是最慘的。過去幾個季度,存儲市場經歷了過去15年來最嚴重的低迷。自2021年第三季度以來,DRAM和NAND芯片價格分別下降了57%和55%。

與之相對應的,存儲芯片廠商無一不在飽經風霜,存儲芯片巨頭的季度營收基本跌去了一半。2022年半導體銷售額ToP5企業中,有三星電子、SK海力士、美光3家存儲芯片廠商。然而,從Omdia近日披露的數據來看,2023年第1季度ToP10榜單中僅剩下三星一家存儲廠商。而上一次SK海力士和美光未能躋身前十還是在2008年。

種種跡象都反應出存儲市場正在經歷“寒冬”。為了控制市場波動、降低庫存擠壓,SK海力士、三星電子、美光科技等存儲芯片大廠紛紛釋出降價、減產策略。

儘管當前存儲市場遭受重創,但長期來看依舊潛力巨大。根據Yole數據預計,2025年存儲芯片收入將增長至超過2000億美元的新紀錄高位。

面對市場週期的波動,儘管存儲芯片大廠在縮減資本開支,降低產能,但圍繞技術創新和產品佈局的步伐從未止步。尤其是韓國存儲雙雄三星電子和SK海力士,雙方的競爭態勢已日趨白熱化。

力爭DRAM、NAND基本盤

從存儲芯片類別看,DRAM約佔存儲器市場53%,NAND Flash約佔45%,二者份額合計達98%,為存儲器市場的兩大標杆產品,也是三星電子和SK海力士展開競爭的“基本盤”。

DRAM:發力先進製程

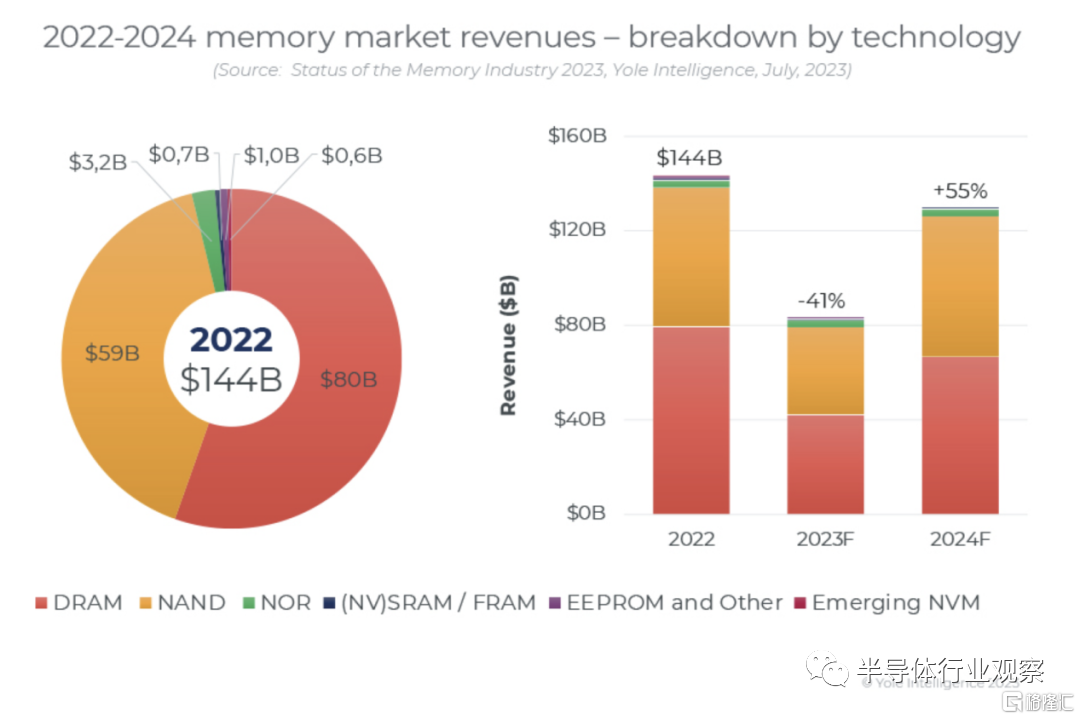

面對DRAM市場的蕭條,行業廠商正在持續研發推出1α、1β、1γ或更先進製程的DRAM產品,嘗試以技術創新在逆境中站穩腳跟。

不難理解,對DRAM芯片而言,先進製程意味着高能效與高容量,以及更好的終端使用體驗。

從存儲巨頭的工藝製程發展歷程來看,在2016-2017年進入1X(16nm-19nm)階段,2018-2019年為1Y(14nm-16nm),2020年處於1Z(12nm-14nm)時代,目前繼續向10nm逼近,最新的1α節點仍處於10+nm階段。後續,行業廠商繼續朝着1β、1γ或更先進技術階段繼續邁進。

2022年10月,三星公佈的技術路線圖顯示,預計2023年三星將進入1βnm工藝階段,即第五代10nm級別DRAM產品(另有消息稱,三星將考慮跳過1β DRAM,直接研發1γ DRAM);同年12月,三星開發出首款採用12nm級工藝技術打造的16Gb DDR5 DRAM,與上一代產品相比,最新的12nm級DDR5 DRAM功耗降低了23%,晶圓生產率提高了20%。今年5月該產品已開始量產。

據瞭解,結合先進的多層EUV光刻技術,這款產品擁有三星最高的DDR5 Die密度,可使晶圓生產率提高20%,功耗有望節省約23%,最高支持7.2Gbps的運行速度。為了搶佔逐漸擴大的DDR5市場,三星計劃從2023年開始批量生產,並向數據中心和人工智能等領域客户供貨。

而SK海力士重點發力存儲產品的運行速度。今年5月,SK 海力士宣佈已經完成了1β 製程技術(第五代10nm 等級) 研發,並將其技術生產的DDR5 服務器DRAM 進行英特爾數據中心存儲器認證程序。

據介紹,SK海力士這次提供的DDR5 DRAM產品運行速度為6.4Gbps,也是同類產品裏速率最高的,與初期的測試品項相比,數據處理速度提高了33%。而且,其採用了HKMG (High-K Metal Gate)製程技術,相較第四代10nm等級的1α製程技術的產品,功耗降低了20%。

SK海力士希望2023年開始量產最先進的1β製程技術產品,以業界最高DRAM競爭力水準改善2023 年下半年的業績。此外,SK海力士還打算1β製程技術延伸到LPDDR5T、HBM3E 等產品上。

三星、SK海力士等DRAM廠商爭相爆出有關第五代1β DRAM的最新研發進展,新一代產品在數據處理速度、功耗、耗電量等方面都有了顯著提升,在移動設備、智能車輛、數據中心以及人工智能等領域的應用將更加廣泛。

與此同時,存儲廠商又開始了對下一代工藝節點1γ DRAM的研發。

業界認為1γ工藝是DRAM接下來的競爭關鍵。賽迪顧問集成電路高級分析師楊俊剛表示,1β DRAM產品主要受存儲市場萎靡影響,市場空間相對有限。預計存儲市場在2023年底或2024年上半年開始反彈,按照DRAM市場技術迭代速度,市場復甦剛好迎來1γ DRAM產品推出時間,所以1γ DRAM產品成為市場復甦後各家競爭關鍵。

三星近期放出的消息也側面應證了這一觀點。三星為了擴大與競爭對手的技術差距,已經要求其研究人員停止或跳過1β DRAM的開發,新的目標是在今年6月前完成11納米的第六代1γ DRAM的開發。

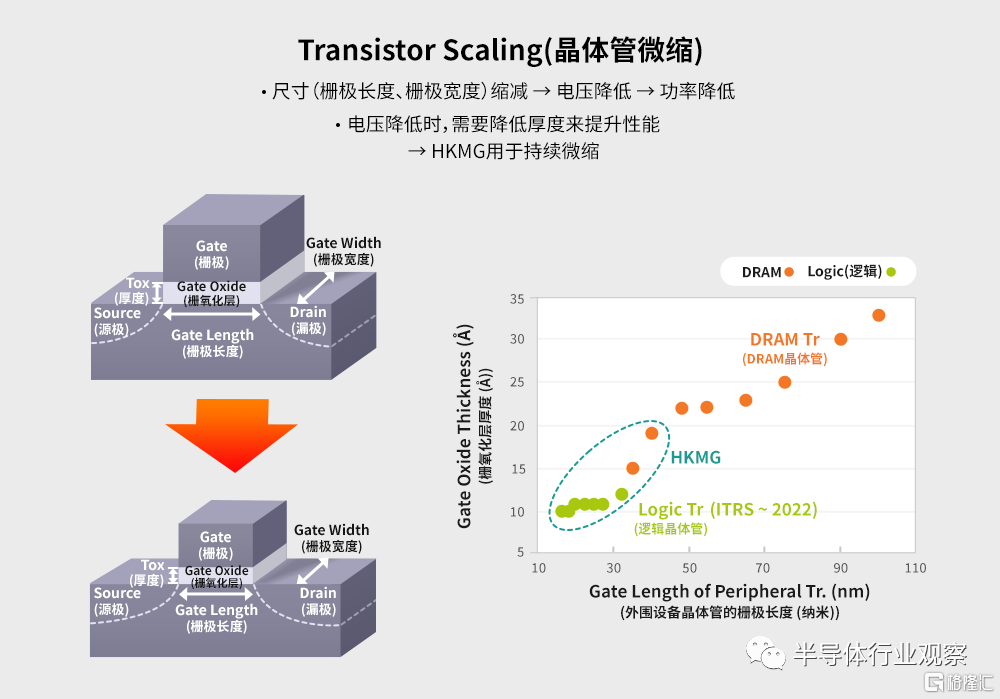

3D DRAM 是一種採用全新結構的存儲芯片。簡單來説,現有DRAM產品開發的重點是通過晶體管微縮來提高密度,但隨着線寬進入10nm 範圍,業界開始面臨電容器漏電和干擾等物理限制。為此,三星、SK海力士等一直在開發圖案化、材料和架構方面的顛覆性解決方案,HKMG(High-k/Metal Gate)則成為突破這一困局的解決方案。

Transistor Scaling(晶體管微縮)

另一方面,3D DRAM順勢成為了存儲廠商迫切想突破DRAM工藝更高極限的新路徑。

三星電子和SK海力士等全球DRAM巨頭正在加速推進3D DRAM的商用化。三星和SK海力士的高管在官方活動上曾表示,都將3D DRAM作為克服DRAM物理極限的一種方式。三星表示,3D DRAM是半導體行業未來的增長動力;SK海力士則認為,大概在明年,關於3D DRAM的電氣特性細節將被公開,從而決定其發展方向。

NAND:芯片堆疊層數之爭

NAND閃存芯片是最主要的存儲芯片,可以實現大容量存儲、高寫入和擦除速度,多應用於大容量數據存儲,例如智能手機、平板電腦、U盤、固態硬盤等領域。

2007年,隨着2D NAND達到規模極限,東芝率先提出了3D NAND結構概念。2013年三星則率先推出了“V-NAND”,也就是3D NAND。其中的V代表Vertical,垂直的意思,這是一種通過垂直堆疊3D空間中的穿孔連接其單元層的解決方案,這種3D設計方式不僅帶來了技術性能的提升,而且還進一步控制了成本。

三星率先將3D NAND閃存從技術概念推向了商業市場。

隨後,V-NAND閃存不斷髮展,每一代新的V-NAND都帶來了顯着的性能提升,以及更低的功耗。2013年三星開發的第一個V-NAND閃存僅有24層,目前三星的V-NAND已經發展到了第8代的236層。

去年11月,三星宣佈已開始量產三星產品中具有最高存儲密度的1Tb三級單元(TLC)第8代V-NAND,其I/O速度高達2.4 Gbps,相比上一代提升了1.2倍,這可以滿足PCIe 4.0和更高版本PCIe 5.0的性能要求。三星第8代V-NAND層數達到了236層。

2023年初,三星還制定了開發新一代3D NAND的計劃:2024年推出的第九代3D NAND有望達到280層;第十代3D NAND有望跳過300層的區間,達到430層,預計將於2025-2026年推出。此外,三星還計劃到2030年推出超過1000層的產品,以更好地支持未來的數據密集型技術。

三星雖是NAND閃存技術的奠基者並在過去一直領導市場發展,但在200層以上的競爭上,SK海力士也表現不俗。

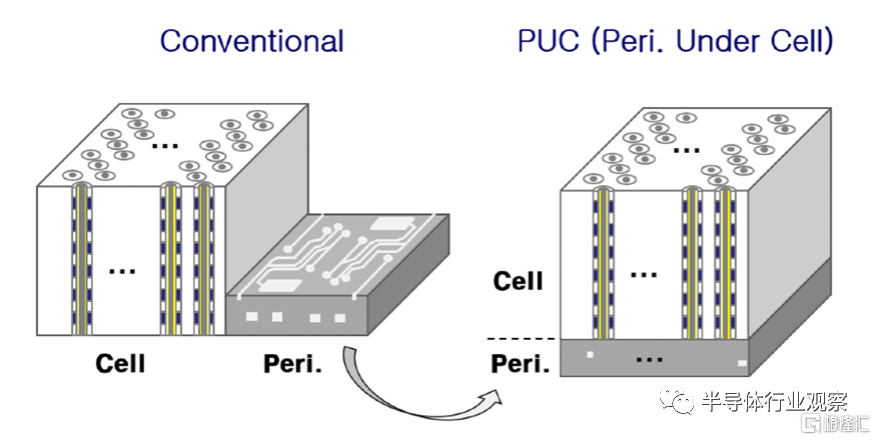

2018年11月,從第四代96層3D NAND開始,SK海力士推出了新的命名法——4D PUC(Periphery Under Cell),PUC是一種將外圍電路重新定位到電池底部的技術,如下圖所示。

相比3D方式,4D架構具有單元面積更小,生產效率更高的優點。為成功研發4D架構的芯片,SK海力士採用了電荷捕獲型技術(CTF)和PUC技術,進而確保了成本、性能、產品質量等層面的全球領先競爭力。

4D NAND(圖源:SK海力士)

98層之後,SK海力士陸續開發出128層、176層3D NAND。2022年8月,SK海力士宣佈開發出最新的238層4D NAND閃存,並已於今年6月開始投入量產。(4D NAND代表的是一種先進性,而不是指進入第四維度)

據介紹,SK海力士的238層NAND閃存成功堆棧更高層數的同時,實現了業界最小的面積,生產效率比上一代的176層提升了34%。此產品的數據傳輸速度為每秒2.4Gb,號稱比上一代的速度快50%,並且改善了約20%的讀寫性能。

在ISSCC 2023會議期間,SK海力士公佈了在3D NAND閃存開發方面的最新突破,展示了其最新300層堆疊第8代3D NAND Flash的原型。

據SK海力士介紹,第8代3D NAND閃存主要運用了五個方面的技術,包括引入三重驗編程(TPGM)功能,可縮小電池閾值電壓分佈,將tPROG減少10%,從而提高性能;自適應未選字符串預充電(AUSP),另一種將tPROG降低約2%的方法;編程虛擬串(PDS)技術,降低通道電容負載來縮短tPROG和tR的世界線建立時間;平面級讀取重試(PLRR)功能,允許在不終止其他平面的情況下改變平面的讀取級別,從而立即發出後續讀取命令,最終提高了服務質量和讀取性能。

SK海力士沒有提供第8代3D NAND閃存的時間表,有行業人士估計,可能要等到2024年末或2025年某個時候才會上市。與此同時,SK海力士的第7代238層3D NAND閃存預計將被整合到2023年推出的新款閃存產品的生產週期裏。

早在2019年,SK海力士就做出過大膽假設,計劃2025年推出500層堆疊產品,並在2032年實現800層以上。

自從NAND閃存進入3D時代,芯片的層數比拼一直是各大NAND閃存芯片廠商競爭的重點,堆棧層數猶如摩天大樓一樣越來越高。在3D NAND技術賽跑中,存儲廠商從最初的24層、32層,一路堆到了128層、176層,直至200+層。層數越高,NAND閃存可具有的容量就越大,增加層數以及提高產量也是衡量技術實力的標準。

縱觀當前全球的閃存格局,層數之爭依舊是NAND閃存的主旋律。各大廠商紛紛採取措施,為儘可能多的佔領市場的進行擴產,正在往更多層數進行技術邁進。

雖然現在還無法預測3D NAND最高可堆疊至多少層,不過隨着頭部企業持續加大3D NAND閃存市場佈局,推動技術創新和演進,3D NAND閃存堆棧高度不斷突破極限。

但需要強調的是,雖然3D NAND未來發展方向是堆棧添加更多的層,但NAND層數的競爭將對製造工藝帶來更大挑戰。正如三星高管所言,為了推動1000層的NAND技術,將面臨穩定性問題,就像建造摩天大廈一樣必須考慮坍塌、彎曲和開裂等因素。此外,他們還必須解決連接孔加工工藝、電池干擾最小化、層高縮短以及每層儲存容量擴大等問題。

“基本盤”之外,競爭再現新高地

除了在DRAM和NAND上的比拼之外,韓國存儲雙雄在GDDR、LPDDR、HBM、PIM、UFS等細分賽道仍展現出新的競爭姿態。

GDDR:GDDR7,釋放下一代顯存潛力

GDDR(Graphics DDR),即圖形DDR,它是為了設計高端顯卡而特別設計的高性能DDR存儲器規格,是打破“內存牆”的有效方案。

去年,三星公佈了為GPU和服務器開發GDDR7 DRAM的計劃。近日,三星宣佈已完成 GDDR7 DRAM芯片的開發,將有助於提升在需要出色圖形性能的領域的用户體驗,例如工作站、個人電腦和遊戲機,並有望擴展到未來的應用領域,如人工智能、高性能計算(HPC)和汽車車輛等。

據瞭解,三星的GDDR7 DRAM擁有破紀錄的1.5TBps帶寬,比GDDR6 DRAM高出40%,能效也比GDDR6 DRAM芯片高出20%。得益於PAM3(脈衝幅度調製)信號方法的增強,它的每引腳速度為32Gbps,比上一代產品高出33%。

三星還為其新芯片提供了較低電壓的選擇,為了減少熱量產生,除了IC架構優化之外,三星還在封裝中使用了具有高導熱性的新型EMC材料。所有這些改進使其熱阻降低了70%,從而提供了更穩定的產品,即使在高壓力的操作條件下也能表現良好。

三星的重要客户將於今年開始測試GDDR7 DRAM芯片進行驗證。但由於沒有來自JEDEC的硬性承諾,因此沒有預計GDDR7發佈的具體時間表。鑑於如今有如此多的AI和HPC公司致力於帶寬需求高的產品,其中一兩家可能會更快發佈依賴GDDR7顯存的解決方案。但GDDR7的大規模採用預計會與AMD和NVIDIA的下一代圖形卡的量產同時發生。

反觀SK海力士,其近年來在GDDR閃存顆粒上的信息披露並不多,而是更多在強調以基於GDDR為接口的DRAM存內計算產品GDDR6-AiM(PIM)及其優勢,此部分放在下文做詳細介紹。

HKMG技術賦能LPDDR

LPDDR指的是Low Power DDR,中文全稱為低功耗雙信道同步動態隨機存取內存,通常以先進封裝技術直接堆在CPU處理器上方,減少通道寬度以及其他一些犧牲部分反應時間的方法來降低體積和功耗。因此,是移動應用場景的主流內存產品。

2022年10月,SK海力士宣佈開始銷售基於HKMG技術的全新1αnm LPDDR5X DRAM, 即便在低功率設置下也實現了晶體管性能的顯著提高。

SK海力士官宣LPDDR5X LPDDR開始銷售

SK海力士的LPDDR5X DRAM是首款在低功耗應用中使用HKMG成功批量生產的產品,通過大尺度微縮,同時利用全新HKMG晶體管構建塊的優勢了,晶體管的性能獲得顯著提升;考慮到HKMG的固有特性和針對HKMG優化的設計方案,可以有效控制泄漏電流,較之上一代產品速度提高33%,功耗降低25%。SK海力士的技術不僅達到行業的目標標準,還因為最低功耗而實現ESG價值最大化。

採用HKMG的效果

藉助HKMG,一層薄薄的高k薄膜可取代晶體管柵極中現有的SiON柵氧化層,以防止泄漏電流和可靠性降低。此外,通過減小厚度,可以實現持續微縮,從而顯著減少泄漏,並改善基於多晶硅/SiON的晶體管的速度特性。

在SK海力士推出LPDDR5X後不久,三星電子也緊接着宣佈稱,其最新與移動處理器大廠高通合作的LPDDR5X DRAM,日前以8.5Gbps的業界最快速度通過了驗證。

三星電子存儲產品規劃團隊執行副總裁Daniel Lee表示,8.5Gbps LPDDR5X DRAM的聯合驗證,使我們能夠將這一高速存儲介質的市場推廣速度加快一年多,這是我們與高通技術公司長期合作取得的巨大成就。

隨着LPDDR內存的使用範圍不斷擴大到智能手機以外的人工智能和數據中心應用,存儲和SoC供應商之間的緊密合作變得更加重要。SK海力士和三星將繼續積極與行業創新者合作,以提高生態系統對未來LPDDR標準的準備程度。

存儲雙雄競逐HBM

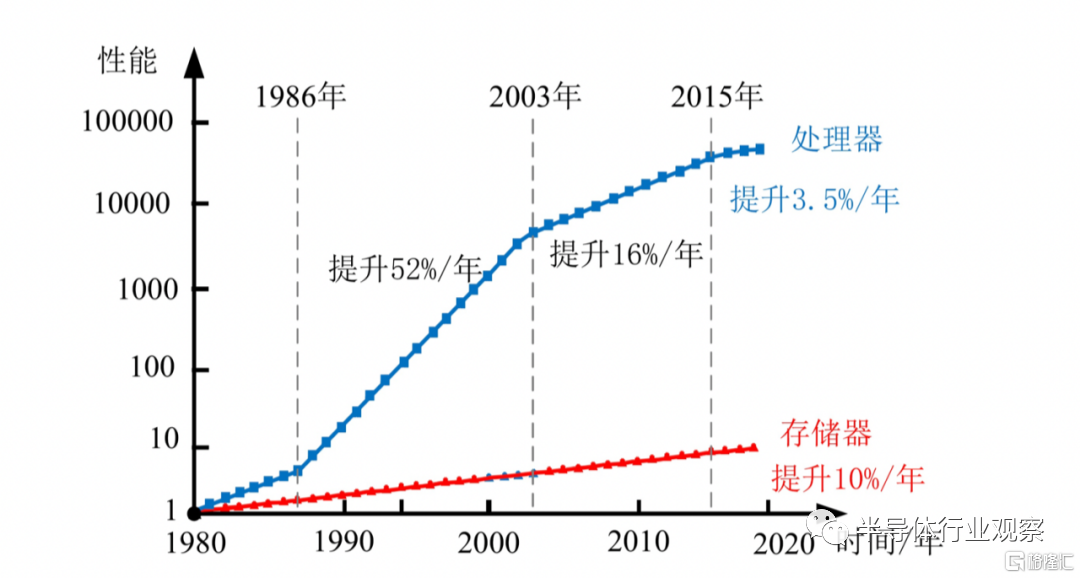

眾所周知,由於處理器與存儲器的工藝、封裝和需求的不同,二者之間的性能差距越來越大。

存儲器數據訪問速度跟不上處理器的數據處理速度,數據傳輸就像處在一個巨大的漏斗之中,不管處理器灌進去多少,存儲器都只能“細水長流”。有數據顯示,處理器和存儲器的速度失配以每年50%的速率增加。

兩者之間數據交換通路窄以及由此引發的高能耗兩大難題,在存儲與運算之間築起了一道“內存牆”。與此同時,隨着數據的爆炸勢增長,內存牆對於計算速度的影響愈發顯現。

CPU與存儲器發展趨勢

為此,業界希望通過增加存儲器帶寬解決大數據時代下的“內存牆”問題,HBM便應運而生。

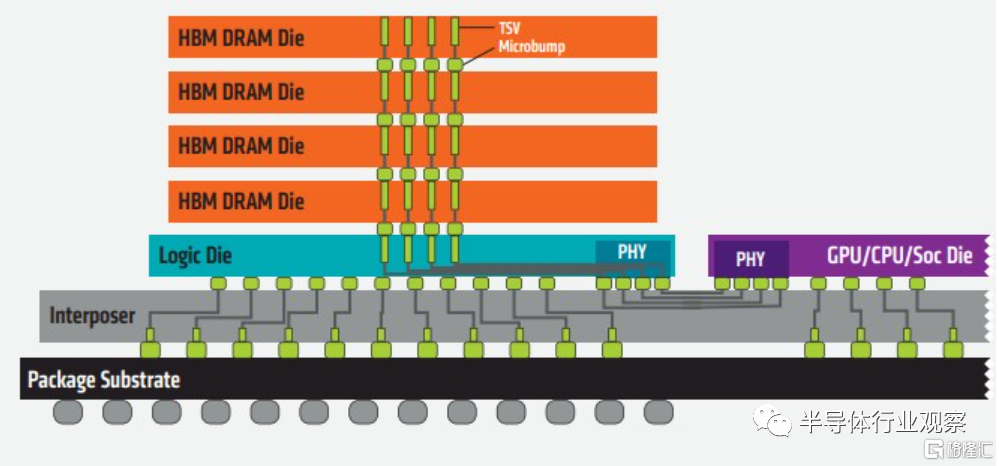

HBM(High Bandwidth Memory,高帶寬內存)是一款新型的內存芯片,其實就是將很多個DDR芯片堆疊在一起後和GPU封裝在一起,實現大容量、高位寬的DDR組合陣列,該技術可以説是DRAM從傳統2D向立體3D發展的主要代表產品,開啟了DRAM 3D化道路。

HBM主要是通過硅通孔(TSV)技術進行芯片堆疊,以增加吞吐量並克服單一封裝內帶寬的限制,將數個DRAM裸片垂直堆疊,裸片之間用TVS技術連接。從技術角度看,HBM充分利用空間、縮小面積,正契合半導體行業小型化、集成化的發展趨勢,並且突破了內存容量與帶寬瓶頸,被視為新一代DRAM解決方案。

裸片之間用TSV技術連接

在內存領域,三星和SK海力士圍繞關於HBM的競賽已悄然打響。

自2014年首款硅通孔HBM產品問世至今,HBM技術已經發展至第四代,分別是:HBM、HBM2、HBM2E、HBM3,HBM芯片容量從1GB升級至24GB,帶寬從128GB/s提升至819GB/s,數據傳輸速率也從1Gbps提高至6.4Gbps。

HBM性能演進(圖源:Rambus)

與傳統DRAM相比,HBM具備高帶寬、高容量、低延時與低功耗等優勢,可以加快AI數據處理速度,更適用於ChatGPT等高性能計算場景。據瞭解,在英偉達A100/H100等高端GPU中,HBM的滲透率接近100%。

SK海力士是HBM市場的先行者,也是全面佈局四代HBM的廠商。2014年,SK海力士與AMD聯合開發第一代硅通孔HBM產品;2018年SK海力士發佈第二代HBM產品HBM2;隨後2020年SK海力士發佈第三代HBM——HBM2E,作為HBM2的擴展版本,性能與容量進一步提升;2021年10月SK海力士成功開發出第四代產品HBM3,並於2022年6月開始量產。

SK海力士今年4月20日宣佈,在全球首次實現垂直堆疊12個單品DRAM芯片,成功開發出最高容量24GB的HBM3 DRAM。該產品容量較上一代HBM3 DRAM提升50%。SK海力士已向客户提供樣品,正接受客户公司的性能驗證。

在AI市場奪得先機,是SK海力士如此迫切地推陳出新的主要原因。值得注意的是,英偉達為SK海力士HBM產品的大客户,英偉達已將16GB HBM3 DRAM搭配A100 GPU供ChatGPT使用,並已將SK海力士的第四代HBM安裝至性能更強的H100 GPU上。SK海力士也按照英偉達的計劃,在去年增加了HBM3 DRAM的產量。

另外,值得關注的是,MR-MUF是SK海力士首先開發的技術,據瞭解目前只有SK海力士使用該技術生產HBM。

SK海力士在近期的投資者活動日中強調,他們已開發出不同於競爭對手的封裝技術(MR-MUF)並以長期獨家的方式從合作伙伴那裏獲得關鍵材料,以此保障了其技術優勢。

MR-MUF封裝是當半導體芯片附着到電路上並且芯片向上堆疊時,用一種稱為環氧模塑料(EMC)的材料填充並附着芯片之間的空間的工藝。之前的競爭對手在此過程中使用了非導電膜 (NCF) 技術。MR-MUF封裝對HBM芯片的外部結構有重大影響。SK 海力士在創建12層HBM3時,將一款產品中堆疊的DRAM數量從8個(16GB)增加到12個,從而將容量增加了約50%。

憑藉這項技術,SK海力士實現了24GB的最大當前容量。SK海力士認為,MR-MUF封裝技術將有效保持其計劃於明年發佈的第五代HBM3E的市場競爭力,超越目前已量產的第四代產品HBM3。

隨着HBM3E需求的爆炸性增長,產量顯着增加。SK海力士決定使用最新的尖端10納米級第五代 (1β) 技術大幅提高明年的產量。大部分增量將由HBM3E填充。這表明SK海力士正在以HBM為首要業務戰略,全力克服半導體低迷。據悉,SK海力士約40%的營業利潤來自HBM。

三星也在積極跟進,三星對HBM的佈局從HBM2開始,目前,三星已經向客户提供了HBM2和HBM2E產品。2016年三星量產HBM2;2020年三星推出了HBM2。

在2022年技術發佈會上發佈的內存技術發展路線圖中,三星展示了涵蓋不同領域的內存接口演進的速度。三星HBM3技術2022年已經量產,其單芯片接口寬度可達1024bit,接口傳輸速率可達6.4Gbps,相比上一代提升1.8倍,從而實現單芯片接口帶寬819GB/s

另據媒體報道,三星已於今年4月26日向韓國專利信息搜索服務提交“Snowbolt”商標申請,預估該商標將於今年下半年應用於DRAM HBM3P產品。

預計三星HBM3P接口速度將高達7.2Gbps,數據傳輸率相比這一代提升10%,從而將堆疊的總帶寬提升到5TB/s以上。HBM3P單芯片和堆疊芯片都將實現更多的總帶寬提升,而這也將會成為人工智能應用的重要推動力,預計在2025年之後的新一代雲端旗艦GPU中看到HBM3P的使用,從而進一步加強雲端人工智能的算力。

集邦諮詢數據顯示,2022年三大原廠HBM市佔率分別為SK海力士50%、三星約40%、美光約10%。

對於市場份額佔比情況,三星電子負責半導體業務的DS部門總裁 Kyung Kye-hyun在7月份的員工內部溝通活動上表示,“三星HBM產品的市場份額仍超過50%”,他駁斥了有關該公司內存競爭力正在下降的擔憂。

無論怎樣,隨着高性能存儲半導體市場有望快速增長,HBM相關市場預計每年增長40%以上,三星電子和SK海力士之間的HBM產品開發競爭仍在升温。

有關HBM未來潛力與演進方向的更多分析內容,在此不過多贅述,有興趣的讀者可查閲筆者此前文章《存儲巨頭競逐HBM》。

PIM,打破芯片“內存牆”

如果是HBM是通過增加存儲器帶寬來解決大數據時代下的“內存牆”問題。那麼,存算一體(PIM)就是另一種解決“存儲牆”與“功耗牆”問題的技術路徑。

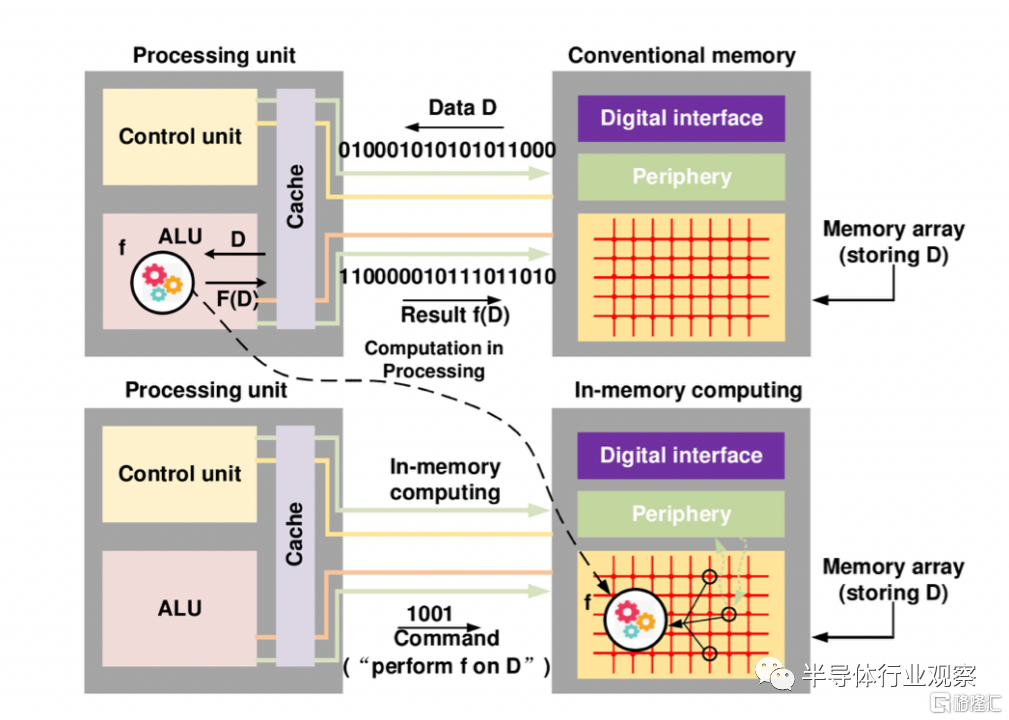

存算一體,又稱存內計算,是一項打破傳統馮諾依曼架構的新型運算架構,通過將存儲和計算有機結合,直接利用存儲單元進行計算,極大地消除了數據搬移帶來的開銷,解決了傳統芯片在運行人工智能算法上的“存儲牆”與“功耗牆”問題,可以數十倍甚至百倍地提高人工智能運算效率,降低成本。

存算一體概念圖

隨着AI的發展數據量暴增,存儲牆、功耗牆成為越來越不容忽視的問題,存內計算已然成為新趨勢。

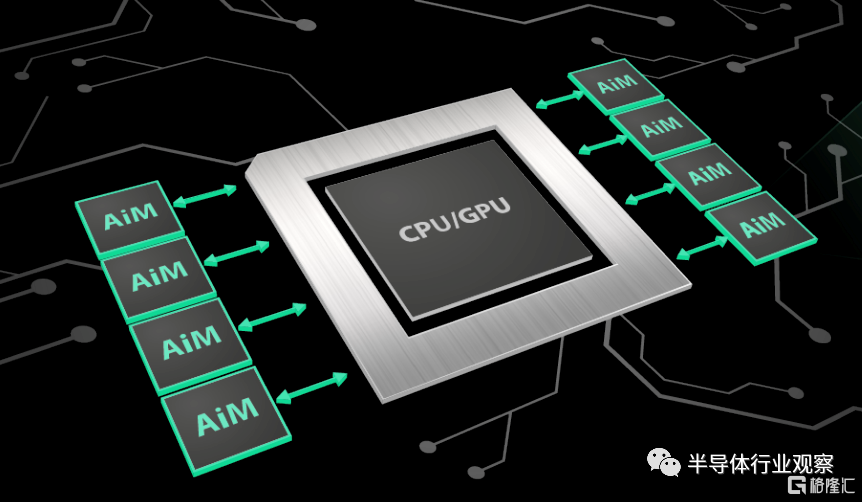

對此,SK海力士開發出了公司首款基於PIM技術的產品——GDDR6-AiM(Accelerator-in-Memory,內存加速器)的樣本。GDDR6-AiM是將計算功能添加到數據傳輸速度為16Gbps的GDDR6內存的產品。與傳統DRAM相比,將GDDR6-AiM與CPU、GPU相結合的系統可在特定計算環境中將演算速度提高至最高16倍。

AiM存內加速器方案(圖源:SK海力士)

此外,GDDR6-AiM的工作電壓為1.25V,低於GDDR6內存的標準工作電壓(1.35V)。不僅如此,PIM的應用還減少了與CPU、GPU的數據傳輸往來,從而降低了CPU及GPU的能源消耗,藉此GDDR6-AiM成功使功耗降低80%。GDDR6-AiM有望在機器學習、高性能計算、大數據計算和存儲等領域有廣泛應用。

SK海力士AiM的另一大優勢在於他們已經實現了全套軟件棧,包括設備驅動、runtime庫、框架和應用等,也支持AiM軟件仿真器,支持用户自行開發AI應用,而無需硬件評估板。

其實三星在PIM上也早有佈局,早在2021年初推出HBM2E後,三星就已經開始規劃如何充分利用這些高帶寬內存的性能,其中之一就是PIM。

與SK海力士不同的是,三星打造的首個PIM為HBM-PIM,在內存核心中了集成了名為可編程計算單元的AI引擎,用於處理一部分的邏輯功能。經過測試,HBM-PIM可推升2.5倍系統效能,且降低逾60%的能耗。

三星表示,HBM-PIM測試結果展現出龐大的商業潛力,隨着技術發展標準化,技術應用將進一步擴大範圍,並延伸至新世代電腦,AI應用HBM3、智能終端移動存儲及數據中心存儲模組。

除了這種將PIM集成到商用AI加速器的方案以外,三星也同時推出了直接將PIM集成到DRAM模塊中的方案AXDIMM,通過直接在DRAM模塊中對多組內存芯片進行並行運算,減少了CPU和DRAM之間的大量數據移動。

此外,三星還在研究基於MRAM的PIM技術,眾所周知,MRAM比DRAM的速度更快,而且運行時更省電。三星在2022年1月12日在頂級期刊nature發表了題為”crossbar array of magnetoresistive memory devices for in-memory computin”的論文,實現了在MRAM上的存內計算

從三星半導體的PIM技術展示也來看,他們也計劃將這一技術應用到GDDR和LPDDR中,不過這幾年間的主要技術公開展示都集中在HBM-PIM上。

寫在最後

儘管半導體產業發展暫時進入“寒冬”,但從韓國存儲雙雄的動態和佈局來看,存儲賽道上的技術競爭仍舊十分激烈。

無論是第五代10nm級DRAM技術,還是更高層數堆疊的NAND Flash,以及HBM、PIM等創新技術,存儲大廠都在積極發力,以保持市場領先地位,並滿足市場對高容量、高性能產品需求,呈現出持續發展的潛能。

與此同時,在複雜的國際貿易關係背景下,三星電子和SK海力士這兩家韓國存儲巨頭,或許還將填補美光被禁後出現的市場空缺,進一步吃到市場紅利,逐漸拉開與競爭對手的身位。