本文來自格隆匯專欄:半導體行業觀察

昨日,韓國存儲廠商SK海力士宣佈,公司第一代使用EUV光刻機生產的DRAM正式量產。

據介紹,公司旗下第四代 10 納米級(1a)製程8Gigabit(Gb)LPDDR4 移動設備專用DRAM已經量產。作爲SK海力士旗下首款採用EUV生產的DRAM,與上一代產品相比,新產品可以將使相同尺寸晶圓生產的 DRAM 芯片數量增加 25%,並能將功耗降低20%。

在更早之前,三星已經率先量產了使用EUV光刻機生產的DRAM,在過去多年稍顯保守的美光也宣佈,將在2024年生產基於EUV的DRAM。至此,三大DRAM大廠都跨入了EUV時代。

DRAM面臨的挑戰

如下圖所示,從原理層面上看,一個最簡單的,存儲一個 Bit 信息的 DRAM Storage Cell 的結構如下圖所示。它主要是由存儲電容(Storage Capacitor)、訪問晶體管(Access Transistor)、字線(Wordline)以及位線(Bitline)四部分組成。

其中,存儲電容通過存儲在其中的電荷的多和少,或者說電容兩端電壓差的高和低,來表示邏輯上的 1 和 0;訪問晶體管的導通和截止決定了允許或禁止對存儲所存儲的信息的讀取和改寫;字線決定了訪問晶體管的導通或者截止;位線則是外界訪問存儲電容的唯一通道。

對於一種這樣設計的器件,如何縮小其工藝尺寸,就成爲了降低DRAM成本和尺寸的關鍵。

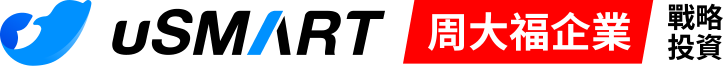

回看DRAM過去多年的發展,在歷經了2008年的40nm級別(表示 49nm 至 40nm,4X4x)、2010 年的30nm 級別(39nm至30nm,或 3x)的推進。自2016年以來,DRAM就一直在10nm級別(19nm到10nm,或1X)徘徊,三大存儲廠商(三星、SK海力士和美光)也都推出了多代的工藝。當中的每一次升級,都涉及在某些維度上減小 DRAM 單元尺寸,以實現增加密度和降低功耗的目的。

DRAM roadmap(source:IEDM 2018)

在後續的發展過程中,供應商在路線圖上還提供了三代規模更大的 DRAM,分別是1anm、1bnm 和 1cnm。雖然供應商尚未透露這些部件的細節,但可以肯定的是它們仍處於 1xnm 節點。同時,我們也清楚認識到,DRAM的微縮面臨新的挑戰。

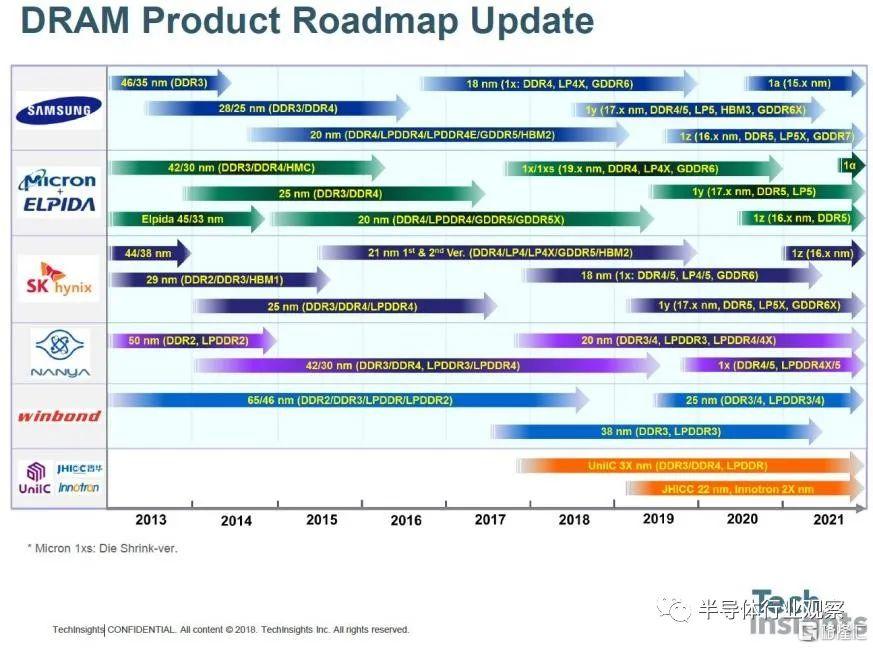

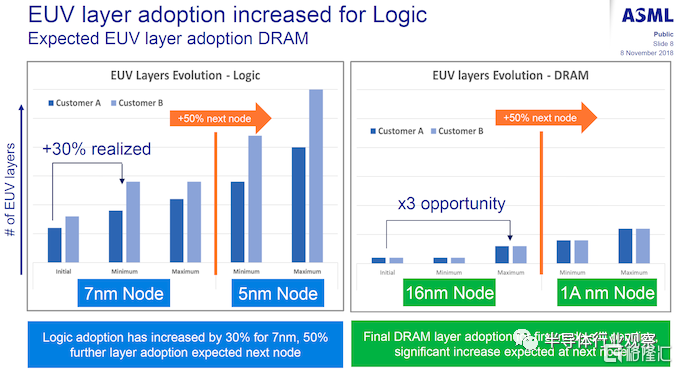

ASML對客戶節點演進的預測

據瞭解,DRAM 的Cell尺寸使用nF²公式進行測量,其中 n 是一個常數,源自cell設計,通常介於 6 和 8 之間,F 是工藝技術的特徵尺寸。因此,特徵尺寸爲 16nm 且 n=8 時,面積爲 8 x (16 x 16) = 2,048 平方納米。如果改用 14 納米特徵尺寸,面積爲 1,568 平方納米,減少 23%。這就是爲什麼縮小特徵尺寸是值得的。因爲通過這個方式,你可以在晶圓上獲得更多 GB 的 DRAM。

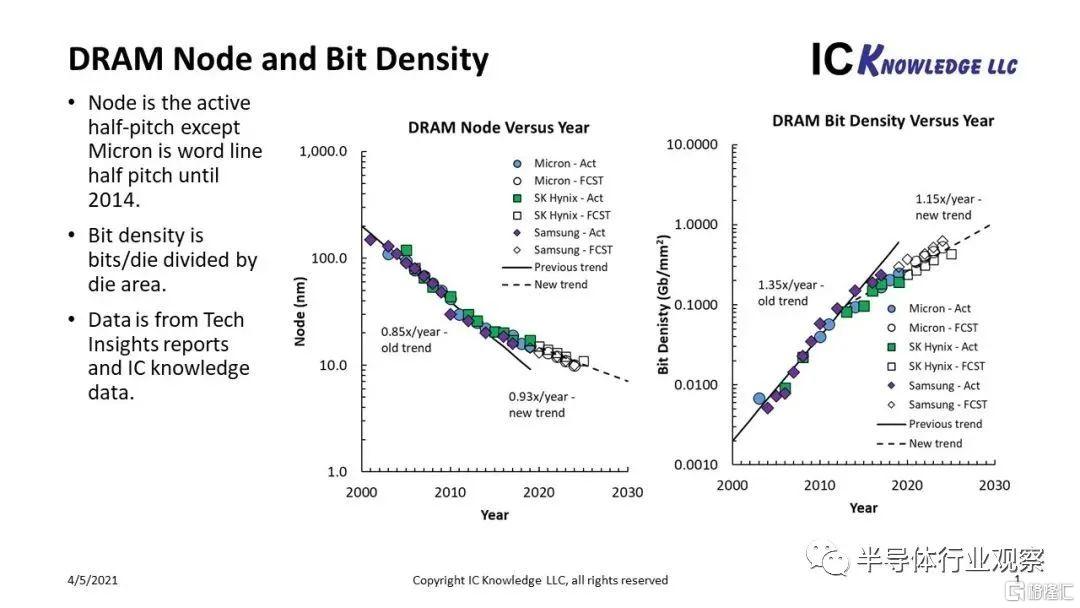

DRAM節點和位密度趨勢

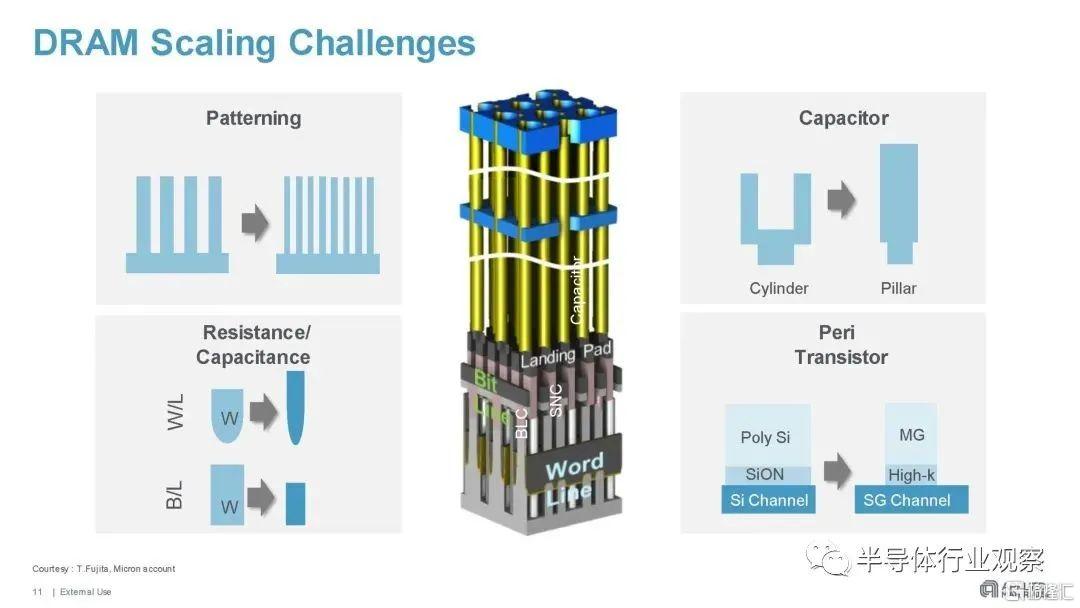

但正如應用材料的Regina在2021年2月舉行的SPIE高級光刻會議上所說,DRAM的微縮正在放緩,爲此需要新的解決方案來繼續提高密度。按照他們介紹,DRAM的微縮迎來了多個方面挑戰:分別是圖案化(如何創建越來越密集的圖案)、電容器(從圓柱體演變爲柱狀結構,需要對高深寬比進行構圖)、電阻/電容(位線和字線需要提高電阻/電容才能提高訪問速度)以及外圍(Peri)晶體管(從含氧化硅的多晶硅柵到高K金屬柵(HKMG)的演變)。

DRAM微縮面臨的四大挑戰

其中,涉及光刻機的電容器圖案化最近已經通過XSADP( cross self-aligned double patterning)完成,但XSADP現在正在發展爲甚至更復雜的XSAQP(cross self-aligned Quater patterning) 。如三星所公開的,另一種選擇是間隔物輔助的圖案化,該圖案化可以使掩模上的孔密度增加3倍,但需要使孔尺寸相等的蝕刻。

爲了實現以上目標,供應商在 1anm 及以後採用不同的路徑。在這些節點上,特徵更小,掩膜層更多。爲簡化流程,DRAM產業首次將EUV投入生產。

爲什麼是EUV?

所謂EUV,也就是Extreme ultraviolet lithography的簡稱。因爲近幾年的科技競爭,大家對這個使用在荷蘭光刻機大廠ASML新型光刻機的技術並不陌生。得益於其波長特性以及先進的設計,EUV光刻機近年來被廣泛應用到先進工藝邏輯芯片的生產中。

但其實根據ASML在2018年的規劃,這也是一種會被存儲領域採用的新技術。

ASML看好的EUV光刻機的機會

SK海力士方面表示,多年來,半導體光刻設備取得了許多進步,採用具有高數值孔徑 (NA) 的大透鏡或使用短波長光作爲光源。然而,隨着柵極長度減小到 30nm 以下,現有沉浸式 ArF 光刻設備的圖案化能力達到了極限。

他們進一步指出,雖然對 18nm 以下的 DRAM 應用了多圖案方法,但這會產生額外的處理階段,並導致生產力損失和材料成本增加,所有這些都導致生產成本不斷上升。由於處理步驟的數量接近 500 到 600 個,唯一的解決方案是通過應用更短波長的光,用“更薄的刷子”繪製微小的電路圖案,EUV就是他們的的選擇。

按照SK海力士的說法,半導體行業一直在準備以 EUV 光刻機實現 10 納米級規模的工藝。通過利用 13.5nm 波長的光,EUV光刻機較之現有的 193nm 的 ArF 實現更精細的半導體電路圖案,而無需進行多重圖案化。藉助這種方式,能將處理步驟的數量減少了,因此製造時間比當前的多重圖案化技術(如四重圖案化技術 (QPT))更短,從而使 EUV 成爲迄今爲止唯一的突破。

三星方面也表示,EUV能夠幫助繪製更精細的電路,因此可以讓芯片在相同的表面積內存儲更多的數據。同時,使電路更精細意味着更多的邏輯門能夠安裝在單個芯片中。通過這樣的方式,就可以讓芯片變得更強大,更節能。在部署 EUV 後,芯片的表面積得到了更有效的利用,爲此,業內的人爭先恐後地爲自己的生產線完善這項技術。

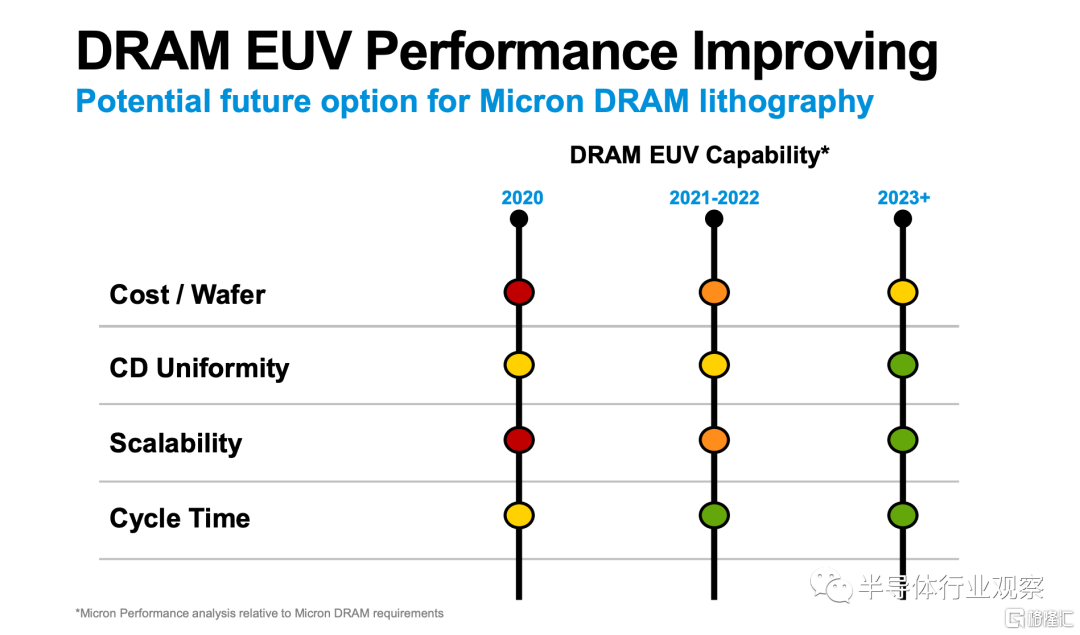

而從美光的介紹我們可以看到,如下圖所示,在DRAM中引入EUV之後,能帶來多方面的優勢。

“使用 EUV,您可以獲得更好的圖案保真度。因爲如果這些掩模層堆疊得越多,您獲得的圖像就越模糊。”VLSI Research 首席執行Dan Hutcheson表示。

三大廠商先後出招

在看到了EUV的機會後,三星、SK海力士和美光這三大DRAM大廠已經先後進入了EUV DRAM市場,或者至少已經公佈了公司的EUV DRAM規劃。其中,三星更是當中的先頭兵。

在2020年三月,他們宣佈推出了業界首款基於 EUV 的10納米級 (D1x) DDR4 DRAM 模塊。三星方面表示, D1x 是一種實驗性 EUVL 製造工藝,用於製造實驗性 DDR4 DRAM,但不會進一步使用。

據三星當時的介紹,面向在今年推出的DDR5 和 LPDDR5,三星將使用其 D1a工藝,這是一種具有 EUV 層的高度先進的 14 納米級工藝。與 D1x 技術相比,該技術有望使每個晶圓的生產率(DRAM 位輸出)翻倍,這表明它使用更薄的幾何結構。

三星方面進一步指出,EUVL 的使用將使三星(以及最終其他內存製造商)能夠減少(或消除)多圖案的使用,從而提高圖案精度、性能和產量。後者將受益於高性能大容量 DDR5 芯片的生產,因爲它們旨在提高性能(高達 DDR4-6400)和容量(高達 32 Gbps)。不過三星併爲正式透露其 D1x 和 D1a 工藝技術使用了多少 EUV 層。

業內知名機構techinsights則在今年三月對三星電⼦量產的EUV DRAM芯片D1z 進行了拆解。據介紹,這個產品應該是在韓國平澤市(Pyeongtaek)的第⼆條⽣產線製造。

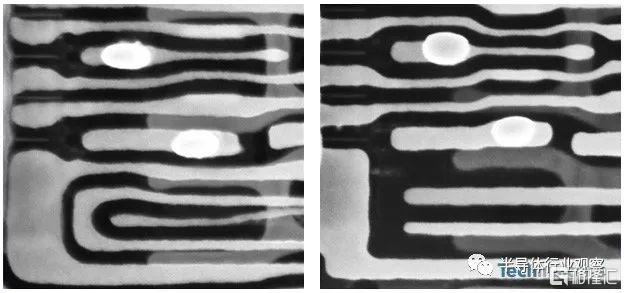

圖1:比較三星的DRAM儲存單元BLP圖案:(a)是不採⽤EUV微影技術的版本

(b)是採⽤ EUV微影技術的版本。

techinsights在報告中進一步指出,在D1z 12Gb LPDDR5元件的製程整合上,三星電⼦只在⼀層光罩上採⽤EUV微影技術,單⼀SNLP (在記憶體單元陣列上)/BLP (在S/A感測放⼤器電路區)的臨界尺⼨(CD/pitch)約40納米,S/A區域的BLP線寬爲13.5納米。

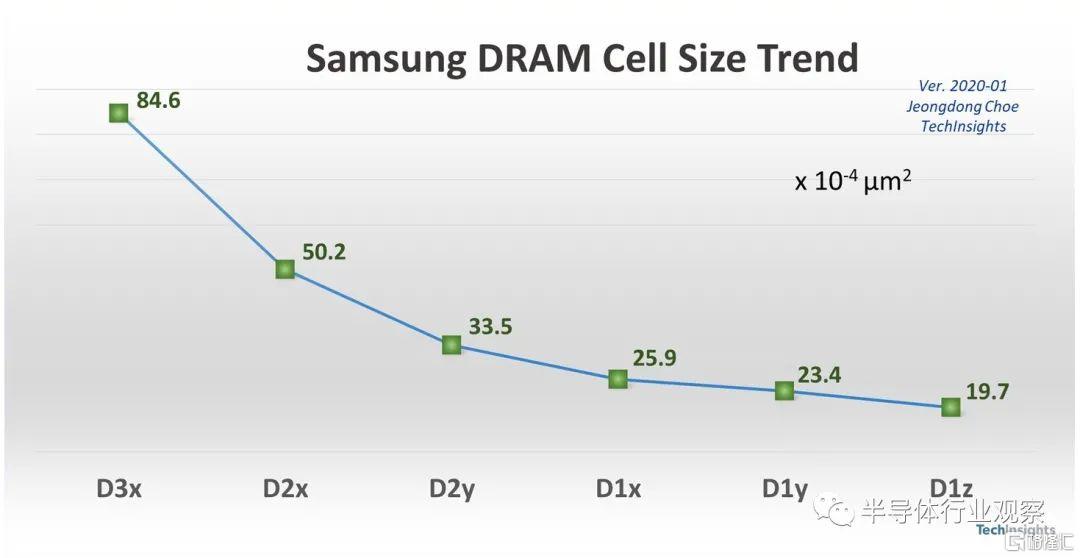

三星DRAM (從D3x到D1z)記憶體單元尺⼨變化趨勢

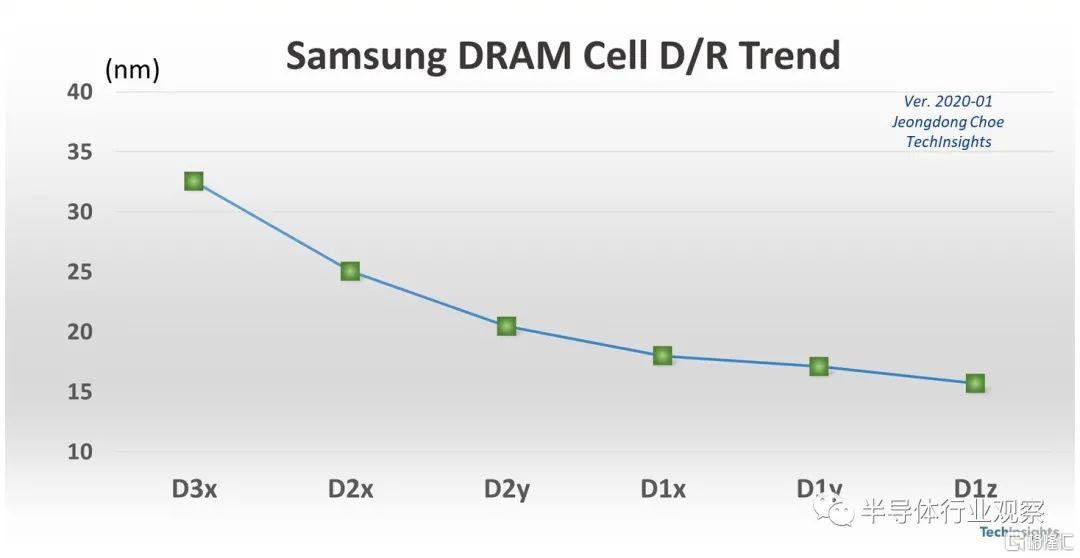

據報告。三星從D3x到D1z的DRAM記憶體單元尺⼨與D/R趨勢變化分別如上圖與下圖所⽰。DRAM 記憶體單元與D/R微縮近年變得越來越艱難,但三星還是將D1z的D/R縮⼩到15.7奈米,比前⼀代D1y減少了8.2%。他們表示,三星將繼續爲下⼀代DRAM產品增加採⽤EUV微影的光罩層數,像是預計2021年量產的D1a與2022年量產的D1b。

三星DRAM (從D3x到D1z)設計規則變化趨勢。

來到SK海力士方面,據報道,在去年五月,他們就開始了一個相當於15nm工藝的EUV DRAM研發。在今年二月,公司完成了其第一條配備了用於 DRAM 芯片的極紫外光刻設備的生產線M16。如上文所說,公司將會首先在1a nm工藝上採用EUV工藝,未來,公司還會將 EUV 的實施擴展到 1b、1c 納米線寬節點。從他們官方的介紹我們可以看到,SK海力士在DRAM中也會是隻用到1層的EUV。而爲了進一步保證EUV DRAM的供給,SK海力士在今年二月還與ASML達成了一個長達五年、總金額達到43億美元的的EUV光刻機供應協議。

至於美光,在多次壓榨DUV之後,並推出基於此的1a nm工藝之後。他們終於按捺不住,宣佈了公司的EUV規劃。

在六月底,美光表示,公司計劃今年年底在其研究設施中安裝 ASML 的新型 EUV 光刻設備 NXE:3600D。公司預計將把新設備應用於量產線進行實驗,然後再正式投入量產。美光CEO表示:“根據我們對 EUV 取得的進展的評估,並與我們的技術戰略和行業領先的 DRAM 擴展路線圖保持一致,我們計劃從 2024 年開始將 EUV 插入到我們的 DRAM 路線圖中。作爲長期批量協議的一部分,美光已向ASML下達採購訂單,以獲取來自來他們的多個 EUV 工具”。

結語

雖然EUV能夠給DRAM供應商帶來不少好處,但正如應用材料的Regina所說,爲DRAM實施EUV面臨以下幾個挑戰:局部臨界尺寸均勻性(Local Critical Dimension Uniformity:LCDU),因爲這種變化會改變電氣性能和蝕刻縱橫比;孔尺寸– EUV對孔尺寸敏感,並且加工窗口狹窄;薄抗蝕劑– EUV抗蝕劑非常薄,需要硬化。

“EUV的一個主要問題是狹窄的工藝窗口;此外,當今的電容器間距極限大於40nm,這也是當前電容器圖案化的EUV極限。將來將需要更小的間距,並且工藝可變性需要提高30%以上,才能實現縮放”,Regina進一步指出。

爲此在他看來,EUV不足夠解決DRAM的微縮問題,這需要我們在3至5年後,引入一種新的DRAM架構。當中涉及的一個有趣的選擇是3D化,那就是將電容器從垂直結構變爲堆疊的水平結構。