本文來自格隆匯專欄:半導體行業觀察

據semianalysis報道所説,大型私營半導體設備公司所剩無幾,其中最突出的兩家是日本國際電氣(Kokusai Electric )和奧地利 EV Group。兩家公司都是令人驚歎的公司,都利用了 Gate All around 邏輯和 3D NAND 的趨勢。就 EV Group 而言,情況非常簡單,用於異構集成和背面電力傳輸的晶圓鍵合機。

國際電氣(“KE”)即將首次公開募股,因此值得進行更深入的研究。今天,我們將深入探討 FinFET、DRAM 和 3D NAND 的製造工藝,以及 Gate All around、CFET 和 3D DRAM 工藝流程即將發生的變化。這些縮放趨勢尤其會嚴重影響沉積、光刻和蝕刻。此次深入研究對於 Lam Research、ASMI、Tokyo Electron 和 Applied Materials 也具有重要意義。為此,ASMI 專門提出了一種説法,但 KE 表明,這種説法並不完全正確。

專注薄膜沉積的國際電氣,ALD 專家

國際電氣(“KE”)長期以來一直是日立集團的一部分,原名日立國際電氣(HKE)。2018年3月,在東京證券交易所單獨上市。HKE有兩個主要業務集團,半導體薄膜沉積工藝解決方案和視頻和通信解決方案。這兩個羣體擁有完全不同的商業模式、產品和客户羣。

2016年,HKE決定重組公司,將各個部門分拆給不同的私募股權投資者。私募股權公司 KKR、HVJ Holdings 和 JIP 等一些參與者也加入了這個行列。2017 年,私募股權公司 KKR 收購了日立國際,支付了23億美元收購整個業務。薄膜工藝解決方案仍由 KKR 100% 持有,而視頻和通信業務則拆分為一家獨立公司。

不久之後,2019 年 7 月,應用材料公司宣佈希望以22億美元收購新的 Kokusai Electric(即僅薄膜工藝解決方案業務)(隨後在 2021 年將報價提高 59% 至35億美元) )。此次收購需經過反壟斷審查,在等待中國當局批准兩年後,AMAT 中止了此次收購。

持有五年後,KKR 轉向通過 KE IPO 退出,KKR 將通過二次交易出售 KE 30% 的股份,KE 不再增發股份或籌集資金。

國際電氣(“KE”)將送死定位為薄膜沉積領域的專家。具體來説,KE 銷售批量沉積工具,特別關注批量原子層沉積 (ALD),這是最具選擇性/最精確的沉積形式。KE 還涉足表面處理領域,但就收入而言,遠遠落後於沉積領域。

他們大約 30% 的收入也與服務相關,但應該指出的是,在 KE 的服務部門中,有一部分是傳統 200mm 設備的銷售。這意味着與其他沉積廠商相比,KE 目前的服務強度較低,這有利於晶圓廠的總擁有成本 (TCO),但可能會拖累財務狀況。話雖如此,KE 的新型小批量工具(mini-batch )的服務附加率是其 4 倍,並且是他們發佈的最佳 TCO 工具。

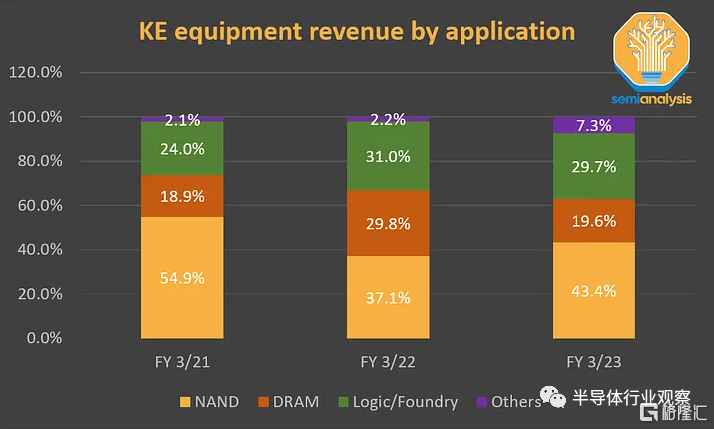

KE 更注重存儲業務,NAND 是其設備最大的應用,其次是 DRAM,然後是邏輯。隨着 Gate All around 的採用,這種情況可能會開始發生變化。

KE 的專長並不涉及所有化學氣相沉積 (CVD) 和原子層沉積 (ALD),而是專門涉及批量batchCVD/ALD工具。其他主要工具製造商(東京電子、應用材料、泛林研究、ASMI)都提供 ALD 工具,但他們主要專注於單晶圓產品,即每個腔室處理 1 個晶圓,而不是多個(batch)晶圓。KE 在批量 ALD 工藝中佔據主導地位,佔據約 70% 的市場份額,其餘部分主要屬於 TEL(以及 ASMI)。

雖然 KE 強調他們在 ALD 領域的份額,但他們仍然接觸批量 CVD 工具。KE 在批量沉積領域的混合市場份額“僅”約為 46%(相比之下,批量 ALD 領域的市場份額約為 70%)。TEL 在總批量沉積市場中僅稍大一些,但我們相信這種情況很快就會發生逆轉,KE 將變得更大。

這是一個非常強大的市場地位,也解釋了應用材料公司想要收購 KE 的原因。AMAT 已經擁有強大的 ALD 產品組合。儘管市場認為 ALD 領導者 ASMI 將完全佔據主導地位並繼續增長份額,但 AMAT 仍擁有許多用於下一代全環柵極 (GAA) 邏輯 ALD 步驟的記錄流程 (POR:Processes of Record )。

AMAT 的專業知識在於單晶圓加工,他們希望將 KE 的批量功能添加到他們的產品組合中。需要明確的是,批量 ALD 與單晶圓 ALD 是完全不同的功能。單晶圓 ALD 方面的專業知識不一定會直接轉移到批量 ALD 工具生產中。AMAT 的收購嘗試實際上是對 KE 在該細分市場的熟練程度的認可。

接下來,我們深入探討 KE 產品背後的底層技術:沉積、ALD 和批處理。

沉積、ALD 和批處理,深入探討

沉積,顧名思義,是將特定材料沉積到晶圓上的過程。雖然我們將芯片稱為“硅”,因為用於芯片製造的基礎基板是硅,但實際上製造的晶圓上存在許多不同的材料。這些材料(通常是不同的金屬和氧化物)通過沉積被放置到晶圓上。

有幾種沉積形式可用於沉積不同的材料:電化學沉積 (ECD) 也稱為電鍍、物理氣相沉積 (PVD) 和化學氣相沉積 (CVD),其中原子層沉積 (ALD) 是其中的一個子集。讓我們快速瀏覽一下。

一、電化學沉積/電鍍

電鍍是一種將金屬薄膜沉積到另一個金屬表面上的常用技術,其基本概念在半導體制造中保持不變。電鍍通常用於沉積銅,例如構建金屬層的互連,或填充硅通孔。將硅片和銅源放置在導電液體浴中。硅片和源都連接到電源。施加電流並且來自電源的電流溶解來自源的離子並將源離子沉積到硅片上。

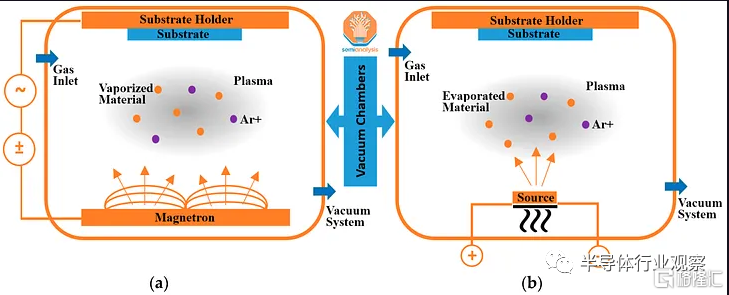

二、物理氣相沉積/濺射

物理氣相沉積 (PVD) 使用等離子體(與等離子體蝕刻的機制類似)從目標材料中產生金屬蒸氣。等離子體的動能使靶材濺射到晶圓上並沉積。PVD 通常用於沉積金屬互連層的阻擋層和銅籽晶以及各種形式的氮化物襯墊。

三、化學氣相沉積

最常見的沉積類型是化學氣相沉積 (CVD)。CVD 通常用於電介質和其他金屬。在 CVD 中,多種前體氣體被排放到腔室中。這些氣體擴散到晶圓上,發生化學反應,形成沉積在晶圓上的材料。

例如,(二)氧化硅是常見的介電/絕緣材料。為了沉積氧化硅,一種方法是將硅烷和氧氣的前體氣體混合,反應生成二氧化硅和氫氣副產物。

四、原子層沉積

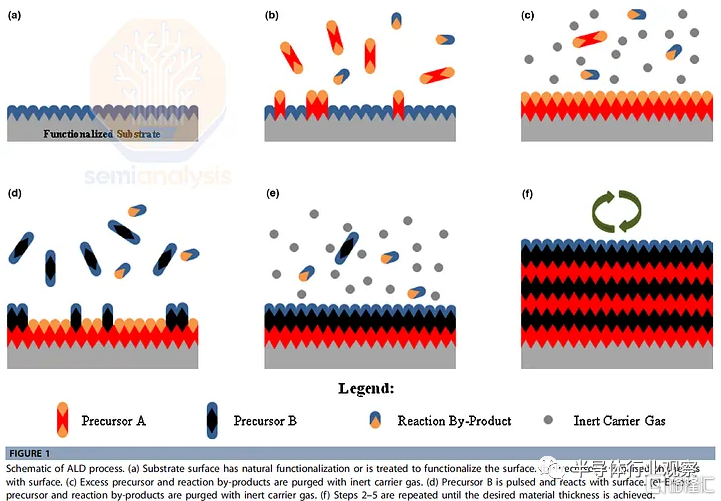

原子層沉積(Atomic Layer Deposition :ALD)是 CVD 的一個子集。在 ALD 中,每次發射一種前體氣體。發射第一氣體以塗覆硅片。然後將惰性氣體(例如 N2或氬氣)流入室中以清除任何過量的先前前體氣體和任何副產物。然後流入第二反應氣體。第二反應物的原子層附着到硅片的表面,其中第一反應物的層和這些元素將發生反應以產生目標材料。重複該過程以形成所需厚度的薄膜。

ALD 的主要特點是它是一個自限過程。一次僅沉積一層原子。一旦表面飽和,前體就不能再沉積。這就是 ALD 作為一種沉積方法具有吸引力的原因。

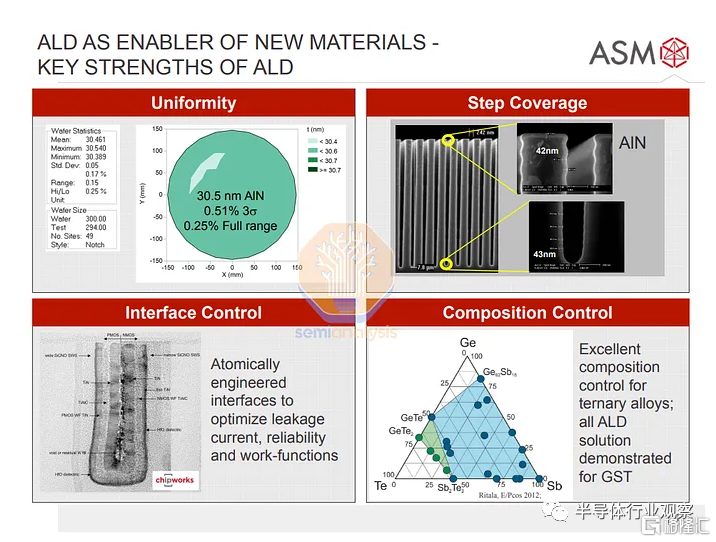

它產生的薄膜具有非常高的保形性、階梯覆蓋性、無針孔,並且允許精確的薄膜厚度控制。這些都是其他形式的沉積所面臨的常見缺陷。ALD 對於更具挑戰性的沉積任務尤其重要:非常薄膜沉積和具有複雜形貌(即非平面表面)的表面沉積,例如 3D 或非常高的縱橫比結構。

基本上,ALD 在沉積質量方面在各個方面都優於傳統 CVD。問題是 ALD 低得多,IE 花費更多的佔地面積、工具時間和金錢。一次僅發射一種氣體前驅物,然後進行淨化處理以去除多餘的前驅物和副產物,這也增加了額外的處理時間。

與一步完成的傳統 CVD 相比,這涉及多個步驟。所有這一切僅導致沉積單個原子層。對於非常薄的薄膜來説,這不是一個問題,但對於較厚的薄膜來説,原子層沉積的吸引力較小。為了解決吞吐量低下的問題,一種解決方案是批量處理此過程。

To batch or not to batch,這是個問題

批處理工具(batch tools)不是一次處理一個晶圓,而是可以處理多個晶圓(有時是數百個晶圓)以提高吞吐量。如前所述,正是 KE 的批量處理能力使他們在 ALD 供應商(ASMI、Lam Research、Applied Materials、Tokyo Electron)的競爭激烈的領域中脱穎而出。

批量處理的好處是顯而易見的:一次處理更多晶圓,從而提高產量並降低工具擁有成本。然而,批處理也有一些缺點、例如,因為腔室要大得多,就很難控制工藝條件。此外,由於腔室內有多個晶圓,可能會出現更多不良相互作用,從而導致缺陷。

如果説兩者有什麼不同的話,那就是在半導體制造的早期階段,批量處理更為普遍。隨着時間的推移,穩定的趨勢是更多地使用單晶圓工具,因為它們在前沿工藝具有更嚴格的工藝公差的世界中提供了更多的控制和靈活性。

對於 ALD 這樣的工藝,批處理具有巨大的優勢,因為它有助於解決 ALD 的主要缺點:吞吐量低。同時,正如我們之前討論的,ALD 還具有自限制特性,使控制成為工藝固有的,並抵消批量工藝可能帶來的較高缺陷率。

關於批量處理需要注意的另一點是,它適合處理大量同質晶圓,這是內存中經常使用的情況,而不是邏輯中的情況。在邏輯上,雖然最大容量的芯片每月確實需要數千個晶圓,在某些極端情況下,需要數萬個晶圓,但在任何特定設計中一次運行數十個晶圓也是很常見的。這意味着批量工具甚至無法飽和,而混合設計意味着該工藝無法針對從計量/檢查收集的特定晶圓數據進行優化。

拋開準確性不談,首先要回答的問題是批量是否真的比單晶圓更具生產力?如果不是,那麼批處理就沒有意義。

雖然從直覺上看,一次批量生產 100 個晶圓比一次處理一個晶圓的生產效率更高,但事實並非如此簡單。與單晶圓處理相比,批量處理會帶來大量額外的開銷,從而增加了週期時間。例如,批量處理使用更大的處理室,因此需要更長的時間才能使處理室糾正温度等工藝參數,並且在沉積後需要更長的時間才能適應晶圓廠環境。

當等效的單晶圓沉積工藝具有更長的處理時間時,這種額外的開銷可以更有效地攤銷,這使得批處理比單晶圓更有效。換句話説,具有某些功能所需特性的晶圓會增加沉積週期時間,這使得更有可能通過批量獲得生產力優勢。

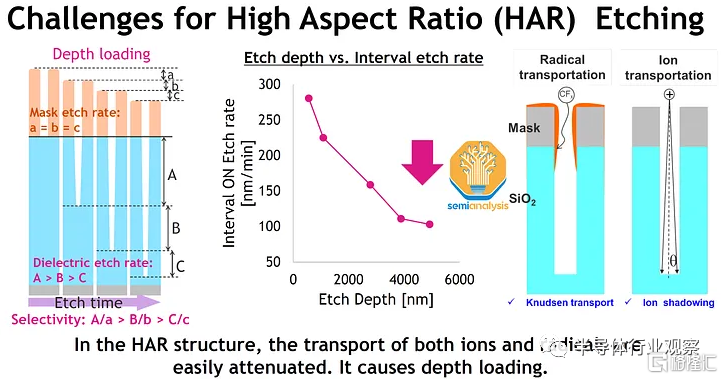

首先,增加沉積時間的主要特徵是高深寬比(“HAR”)結構。縱橫比是高度相對於寬度的比率:因此更深和更窄的結構被認為是高縱橫比結構。HAR 結構大大增加了需要沉積的暴露表面積。同樣,較大的牆壁()需要更長的時間才能塗上一層新油漆,較大的表面積將需要更長的時間才能被原子飽和。

另一個原因是深度加載(depth loading),我們將其視為 NAND 蝕刻的挑戰,以及東京電子為何能夠從 Lam Research 獲得 3D NAND 市場份額的原因。同樣的原則也適用於沉積。基本上,氣體穿透又深又窄的溝槽需要更長的時間。然而,與蝕刻不同的是,該解決方案不在低温下執行該過程,因為 ALD 需要在高於室温的温度下進行。

KE 有一個大型批量工具——AdvancedAce 。該工具一次最多可以批量處理 175 個晶圓(這僅適用於 CVD,而不是 ALD),而 Tsurugi 實際上是一個“小批量”工具,一次最多可以批量處理 50 個晶圓。時間。小批量的原因是,它是一個較小的腔室,與較大的腔室相比,達到工藝參數(例如加熱和冷卻)所需的時間更少,並且提供更高的氣體流速。這可以提供開銷時間和沉積時間的更好平衡以優化最終吞吐量。

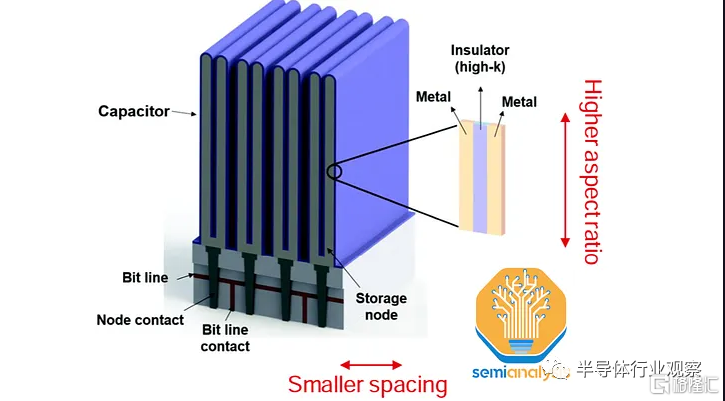

我們通常在內存中看到高縱橫比結構,而不是邏輯結構。對於 NAND,這是縱橫比 >70:1 的溝道孔。DRAM 還具有用於電容器的高縱橫比溝槽。

典型的例子是,由於工藝吞吐量足夠高,批量 ALD 的吞吐量低於 48 層 3D NAND 的單晶圓。由於深度加載,兩者在 64 層時變得相當。除此之外,隨着兩者之間的差距不斷擴大,批處理對於更高層來説變得更加高效。為什麼?更多層意味着更高深寬比的溝道孔。孔的深寬比越高意味着加工時間越長。較長的處理時間使吞吐量方程翻轉,有利於單晶圓的批量處理。

還有其他因素使得批處理在內存中更加普遍。批量工具的停機時間更長,因為腔室僅在裝滿後運行。晶圓可以閒置在處理室中,等待其他晶圓在沉積之前完成其他準備步驟。這在存儲器中不是什麼問題,因為與運行多個不同晶圓的邏輯代工廠相比,晶圓的同質性很高。

對於邏輯而言,一次性工具的靈活性和快速循環時間允許工藝條件的更多變化,從而加快研發和原型設計。在許多情況下,代工廠只想運行幾片晶圓,這一概念被稱為“hot lot ”,這是英特爾使用過多的概念,導致他們花費了數十億美元。這會降低利用率,但會盡快讓設計團隊和產出團隊獲得數據。設計迭代、合格樣品或調整工藝參數以提高產量是一場持續的邏輯鬥爭。

與邏輯和代工廠相比,內存工廠對成本更加敏感,因為內存是一種商品。歸根結底,成本是商品的唯一區別因素。在內存中,該過程經過微調,然後您會運行數十萬個該產品多年。

此外,與邏輯晶圓相比,存儲晶圓要便宜得多。領先的邏輯晶圓每片價格在 20,000 美元左右,如果批量生產 175 個晶圓並且工藝無法正常工作,那就非常昂貴。

原子層沉積的應用

ALD 最適合在哪裏使用?一般來説,ALD 用於具有複雜形貌的結構,尤其是高縱橫比或 3D 的結構,或用於非常薄的薄膜。對於關鍵薄膜,關鍵是實現良好的“階梯覆蓋”(step coverage):即確保在不平坦的基材上沉積具有均勻的厚度。當製造工藝變得更加 3D 時,步驟覆蓋就更難實現。如果您嘗試填充深溝的牆壁,則底部的填充速度與溝口附近的牆壁的填充速度相同非常重要。

如今,所有 NAND 閃存都是 3D,因此我們看到很多 ALD 用於它。邏輯正在變得更加 3D,結構周圍有門,路線圖上有 3D DRAM。從結構上講,這意味着整體上具有更高的蝕刻和沉積強度。同樣,3D NAND 的光刻強度也有所下降。

具體而言,我們先看一下ALD在3D NAND的應用。

首先,我們將氧化物和氮化物薄膜的交替層沉積到基礎硅片上。每層厚度在 20 至 30 nm 之間。每個堆疊的理論極限可以超過 250 層高,接近 7 微米高。然後添加厚硬掩模,為高深寬比 (HAR) 溝道孔蝕刻做好準備。這種反應離子蝕刻工藝可挖出一系列深度為寬度 70 倍的孔。過道孔的圓度和整個孔深度的均勻性對於減少存儲單元性能的變異性至關重要。對於具有multiple decks的設計重複這些步驟,然後將它們堆疊在一起。

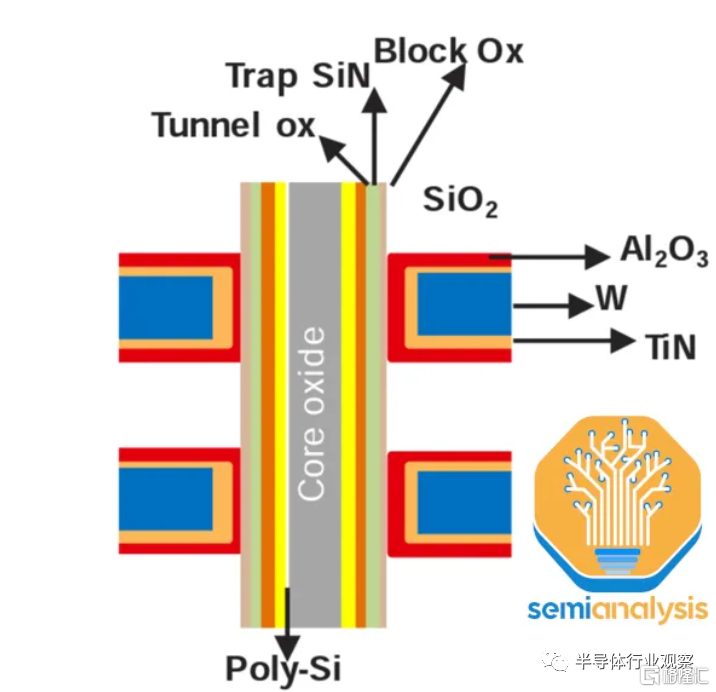

由此,溝道孔被多層填充以形成電荷陷阱單元,每一層沉積在側壁上使孔逐漸變窄。接下來是金屬替代柵極工藝。穿過所有層蝕刻狹縫以形成暴露堆疊側面的溝槽。這樣可以進行氮化物層的折返以及隨後通過 ALD 和鎢字線填充完成的勢壘沉積。在陣列的側面蝕刻出階梯,以使字線層暴露於垂直接觸。

最後,位線和金屬互連形成在上面並與製造的CMOS電路連接,其中包括字線驅動器和用於NAND接口的其他外圍電路。由此我們可以看出,3D NAND 高度依賴於 HAR 蝕刻和沉積能力來擴展密度和性能。

NAND 蝕刻受到廣泛關注,但請注意,也有大量沉積。

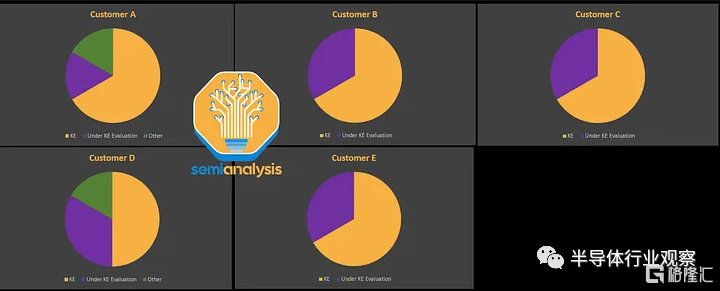

下圖是 3D NAND 存儲單元的橫截面。你可以看到使用了很多不同的材料。有六種薄膜需要 ALD:阻擋氧化物、電荷陷阱氮化物、隧道氧化物、溝道硅。這是除了基礎硅層和字線中的鎢填充之外的。對於阻擋氧化物、電荷陷阱氮化物和隧道氧化物,KE 的批量 ALD 是所有前 5 名 NAND 廠商中創紀錄的工藝工具。對於溝道硅、阻擋金屬和勢壘金屬,KE 到處都有,但實際上 KE 主導了前 3 個步驟。

通常,當談到半導體制造商之間的競爭話題時,我們會説市場很複雜。很難將沉積僅歸類為一個市場,因為存在許多不同的細分市場和利基市場,每個細分市場和利基市場都有自己的領導者。人們意識到競爭少了很多。這是一個很好的例子。對於這幾個特定的NAND 沉積步驟,KE 顯然占主導地位。

其次,DRAM也開始擁抱ALD。

在DRAM中,高縱橫比的特徵是電容器。每一位數據都以負電荷或正電荷的形式存儲在電容器中。每個電容器都連接到一個晶體管,該晶體管控制對電容器中數據的訪問。這是 DRAM 所基於的單晶體管、單電容器 (1T1C) 存儲單元架構。

電容器本身是一個具有高縱橫比的長圓柱形結構。它充滿了金屬-絕緣體-金屬堆疊。絕緣體是高 k 二氧化鋯,可防止泄漏,同時保持電容。由於需要在高深寬比結構中形成良好控制的保形薄膜,因此這種 MIM 堆棧需要 ALD。這就是KE在DRAM領域擁有強大影響力的一步。例如,我們知道 KE 的批量 ALD 用於三星的高 k 沉積的某些部分,也可能與其他 DRAM 製造商一起使用。

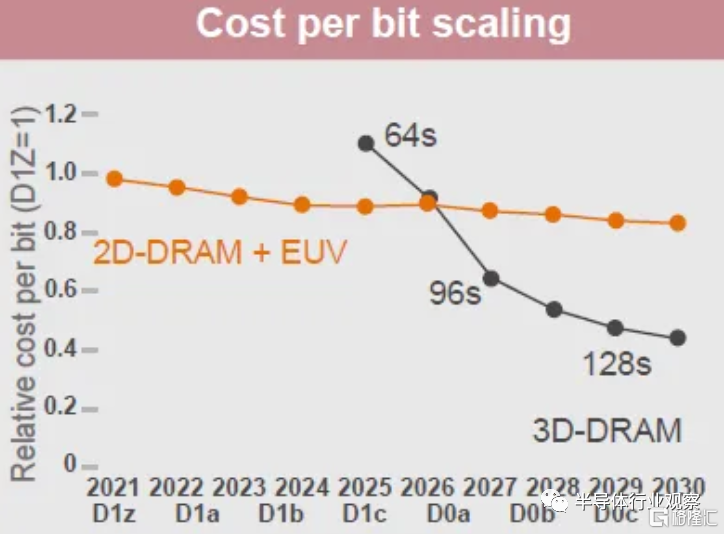

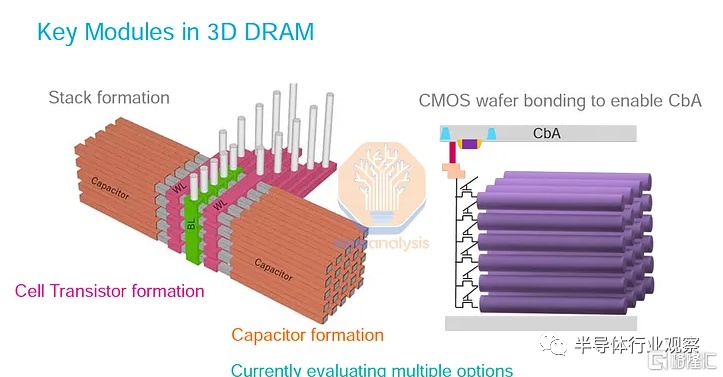

目前,進一步縮小 DRAM 的關鍵挑戰是縮小電容器的尺寸。電容器的任何進一步縮小都會使電容器無法保持電荷,從而變得無用。與 NAND 一樣,3D DRAM 被提議作為未來架構,以實現持續的成本擴展。

大多數設備製造商認為 3D DRAM 將在本世紀下半葉實現量產(ASML 除外,堅持認為 3D DRAM 的生產時間要遠遠超過 2030 年)。由於幾乎沒有潛在的可行架構,因此尚未確定確切的 3D DRAM 架構是什麼樣子。這對 ALD 和 etch 來説是一個機會,但對某些工具製造商來説也是一個威脅,因為這將導致市場份額的重新洗牌。

最後,邏輯也成為了ALD的目標。

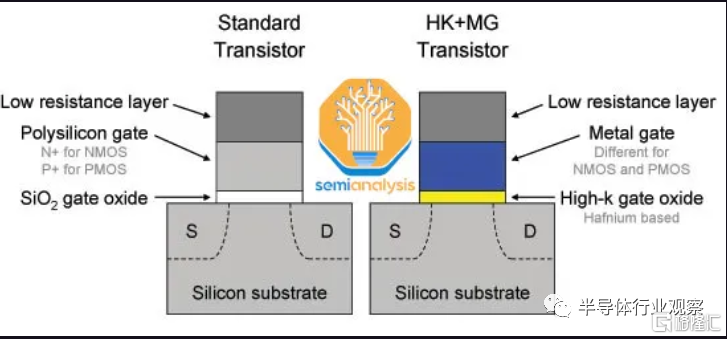

ALD 首次主要進入邏輯製造領域是在 2007 年,當時英特爾於 2007 年在其 45 納米工藝中引入了 ALD。此前,二氧化硅用於柵極絕緣體。隨着特徵尺寸縮小,二氧化硅層也縮小,但人們發現,在 2 納米左右的厚度下,二氧化硅無法正確隔離電流。

英特爾的 45 納米節點引入了革命性的高 K 金屬柵極 (HKMG) 結構,該結構大大減少了電流泄漏,並且是擴展到 65 納米節點以上的關鍵支持功能。HKMG結構用氧化鉿取代了傳統的絕緣氧化硅,並使用金屬代替多晶硅作為柵極。高 K 電介質是通過 ALD 實現的。鉿膜需要高度保形、無針孔,並嚴格控制厚度,以實現其絕緣目的,而這非常適合 ALD 的任務。此外,ALD 也勝出,因為更標準的 CVD 工藝留下了多餘的顆粒用於氧化鉿沉積。

然後,隨着邏輯進入 FinFET 時代,晶體管變為 3D(而不是平面),對 ALD 的需求進一步增加。我們可以看到,對於 FinFET,柵極在三個側面上環繞溝道,並像鰭一樣突出。其效果是柵極可以更好地控制流過晶體管的電流,從而減少泄漏,並且需要更低的電壓來為晶體管供電。柵極氧化物也包裹起來,不再是平面薄膜,這使得實現階梯覆蓋變得更加困難。雖然這項任務已經由 ALD 處理,但我們可以看到,這種新的更具挑戰性的拓撲只會使 ALD 更適合該任務。

總的來説,在邏輯上我們看不到像內存中那樣高的縱橫比的結構。儘管如此,台積電仍然使用批量ALD,台積電是KE的第二大客户。有些薄膜需要 ALD,但更簡單(與使用 ASM 單晶圓工具的非常複雜和關鍵的薄膜相反),並且每個晶圓需要多次重複進行工藝,因此在考慮總擁有成本時,批量處理是有利的。

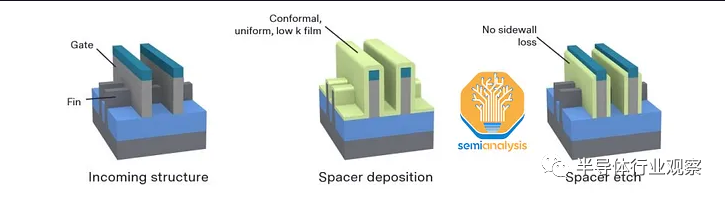

在這種情況下,與 ASMI、Lam Research 和 AMAT 的專用單晶圓工具相比,KE 和 TEL 的批量 ALD 工具更像是主力沉積工具。其中一個例子是批量 ALD 用於沉積 FinFET 柵極側壁上的間隔物。間隔物的目的是減少柵極之間的電容,並且是低k薄膜。

正如您所看到的,間隔物需要沉積在突出柵極的頂部,與柵極和溝道之間的高 k 電介質相比,其縱橫比相對較高。

這就是邏輯上批處理和 KE 工具的用武之地。批量 ALD 非常適合的另一個功能是用於溝槽隔離的間隙填充。淺溝槽隔離是一種用於防止各個電路之間不必要的機電干擾和寄生泄漏的技術。溝槽是通過蝕刻工藝創建的,然後填充二氧化硅等電介質,可以通過批量 ALD 完成。

對於 FinFET,我們發現將柵極包裹在溝道的 3 個側面可以改善電氣特性,那麼所有四個側面的覆蓋不是會更好嗎?基本上,是的,這樣會更好。這是下一代全柵 (GAA) 晶體管架構的方法。通道變成門內一系列多個垂直堆疊的納米片。現在,柵極在所有四個方向上環繞溝道,而 FinFET 中只有三個方向,從而允許更大的驅動電流和泄漏控制,從而改善功耗。

仔細觀察柵極,它實際上是圍繞每個納米片(在下圖中表示為“Epi Si”)的高 k 金屬柵極堆疊。控制閾值電壓需要多個偶極子和功函數金屬層。

ALD 是沉積這些薄膜所必需的,因為它們必須很薄才能全部裝入如此不斷縮小的門內。由此可見,與 FinFET 相比,GAA 需要更多的 ALD 步驟。