本文來自格隆匯專欄:半導體行業觀察;作者:Yole

隨着半導體前端節點變得越來越小,設計成本快速增加。在這種情況下,先進封裝及其 2.5D 和 3D 解決方案在降低與前端製造相關的成本影響方面變得至關重要且有效,同時還有助於提高系統性能並提供更低的延遲、更高的帶寬和電源效率。

根據 Yole 的定義,如果一個die能在每平方毫米內能集成超過16個pitch小於130μm的I/O。如超高密度 (UHD) 扇出、嵌入式硅橋、硅中介層、3D 堆棧存儲器(例如 3D NAND)、高帶寬存儲器(HBM)和 3D 堆棧 DRAM 就是滿足這些標準的一些封裝平台(圖1)。

圖1

另一個值得考慮的平台是 3DSoC,它採用芯片到晶圓 (D2W:die-to-wafer) 的混合鍵合。嵌入式硅橋(embedded Si bridges)有兩種可能的選擇:第一種,稱為 EMIB,由 Intel 提出並嵌入IC基板中;第二種是嵌入模製化合物(mold compound)中的硅中介層,由 TSMC (LSI) 和 SPIL (FOEB) 提供。

具體到硅中介層( Si interposers)方面,則有兩種產品:一種是傳統的或非有源的,通常由 TSMC、三星和 UMC 提供;另一種是有源的,即英特爾的 Foveros。把EMIB 與 Foveros 結合則產生了 Co-EMIB,這個技術被應用到了英特爾的 Ponte Vecchio處理器上。三星、SK海力士和美光則提供了3D 堆疊 DRAM 和 HBM 內存。

值得一提的是,長江存儲是迄今唯一一家使用晶圓對晶圓(W2W:wafer to wafer) 混合鍵合技術生產 3D NAND 的公司。但包括鎧俠和上述三家公司在哪的競爭對手都在考慮進攻這項技術。

此外,Sony(自2015年起)和OmniVision(自2022年起)這樣的CIS供應商使用W2W混合鍵合生產的CMOS圖像傳感器也是一種3D堆疊封裝平台,但它們不是高端性能平台,因為它不能滿足I/O方面密度和間距的要求 ,這代表着其與上述封裝有着相當的差距。

前途無量的先進封裝市場

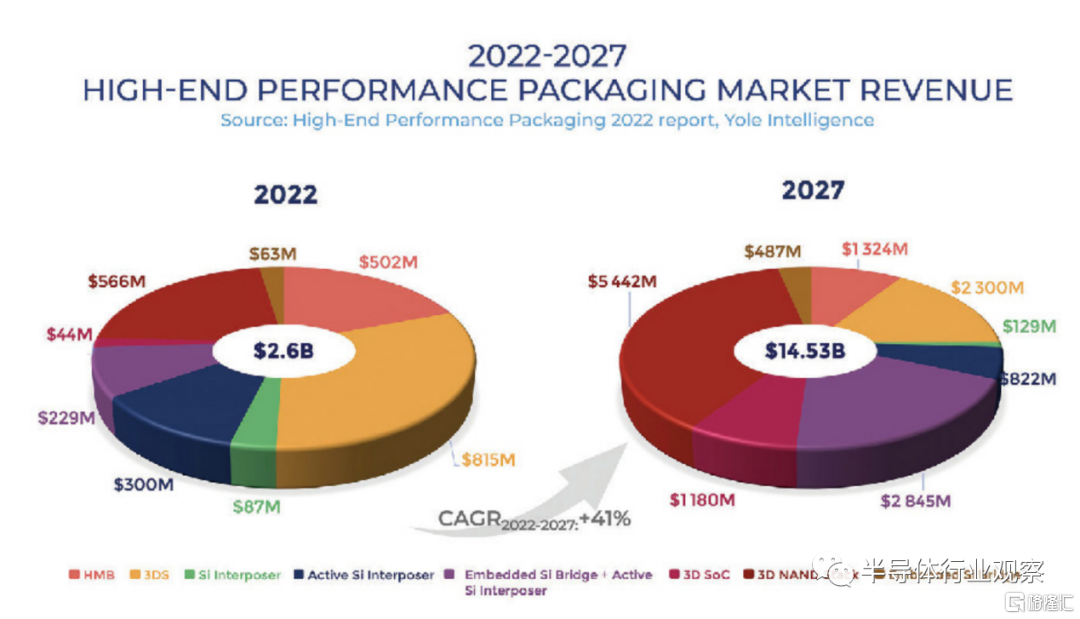

與其他封裝平台相比,高端性能封裝的單位數量很小,但由於其複雜性導致平均售價較高,因此它產生的收入比例更高。預計到 2027 年收入將超過145億美元,高於 2022 年的 26億美元,這就意味着其在2022到2027年間的CAGR為41%(圖 2)。

圖2

這種健康增長歸因於包括雲計算、網絡、人工智能、自動駕駛、個人計算和遊戲在內的高性能計算終端系統的增加。這些應用都需要用更復雜的節點生產更大、更復雜的芯片,這些節點會隨着成本的增加而擴展。這些趨勢促使半導體行業制定具有高端封裝選項的系統級擴展策略,而不僅僅是擴展 FE 高級節點。

通過將大型單片 SoC 裸片拆分成更小的芯片並僅縮放最關鍵的電路組件,小芯片以及異構集成是降低縮放成本的一種選擇。這隻能通過使用具有高連接密度、高帶寬和良好功率效率的 2.5D 和 3D 集成技術來實現。因此,由於研發和生產方面的重大進步,微凸塊、硅通孔 (TSV)、銅柱和混合鍵合正在推動高端性能應用中的 IO 密度和功能集成達到新高度。

3D SoC(包括die-to-wafer和die-to-die混合封裝)則被看作是10μm以下pitch技術的下一個突破點。作為前端封裝技術,這使得高端系統級性能與3D DRAM的更密集的3D IC堆疊、異構集成封裝和封裝分區SoC die成為可能。領先的供應商,尤其是台積電、三星和英特爾,都以此為目標,提供或計劃提供尖端的混合鍵合解決方案。這也許是半導體和封裝世界之間的真正接觸點。

先進封裝正在向前端靠攏。證據在於代工廠和 IDM,因為它們正在成為市場上最先進的2.5D 和 3D 封裝解決方案領導者。OSAT 正努力順應這一趨勢,提供創新的先進封裝解決方案,以幫助解決摩爾定律放緩帶來的前端挑戰,但他們要打入混合鍵合市場將是極其困難的,因為他們缺乏前端能力和必要的資源。

當然,我們也必須承認,沒有事情是百分百的。

拆解當前的先進封裝市場

封裝技術不斷髮展,以滿足日益增長的芯片集成度和對每個組件更高性能的需求。芯片封裝已經完成了從其傳統用途的演變。在傳統用途中,芯片封裝僅用作芯片保護。現在,封裝的設計選擇在解決縮放的減速和滿足對高性能的多樣化需求方面起着至關重要的作用。

通過2.5D&3D異構封裝技術也實現了更小的佔用空間和超高佈線。

最近,新的參與者進入了先進封裝解決方案領域,以提高其高端產品的性能。各種架構和功能也用於增強die之間的互連。例如,硅通孔與die之間的垂直連接已成為一種有吸引力的解決方案,可用於減小封裝尺寸、提高信號完整性並在 HBM 存儲器中提供更高的數據傳輸速率。傳統的銅微凸塊用於創建短而快速的芯片到芯片或芯片到基板的互連。儘管縮小凸點(bumps)變得越來越困難,但一些廠商已經推出了一種使用混合鍵合的新解決方案,以提供直接的、更高密度的互連和可擴展的互連間距。

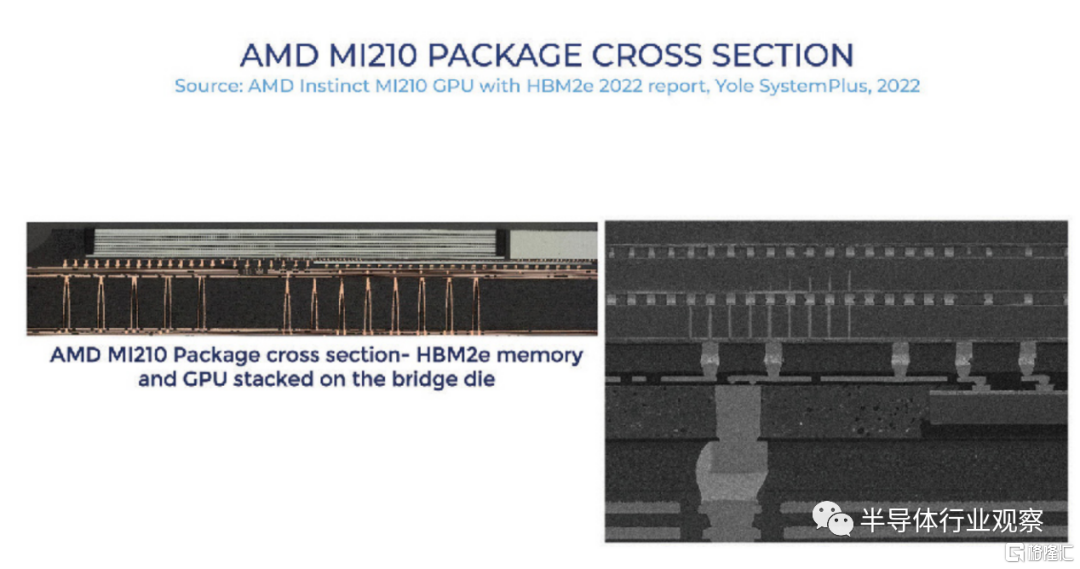

Yole 對先進封裝市場最近出現的各種封裝解決方案進行了分析和比較並發現:NVIDIA 的 A100 使用 TSMC 的大型硅中介層連接 GPU 和 HBM 內存,從而優化了佔用空間並提高了組件性能;然而,中介層的成本相對較高,因為封裝中超過 50% 的芯片全部對應的中介層芯片。面對這些挑戰和硅中介層工藝的成本影響,一些製造商(如 AMD)使用替代解決方案(例如模製中介層 (mold interposer))來減小硅芯片的尺寸和成本。AMD 的 MI210 組件將芯片集成在扇出高架橋接( fan-out elevated bridge technology)技術中,其中多個橋接芯片將處理器裸片連接到 HBM 內存(圖 3)。橋接芯片嵌入封裝成型中,HBM 和 GPU 裸片堆疊在模具中介層( mold interposer)上,銅柱結構穿過成型件,用於將信號從裸片垂直傳輸到基板。該解決方案提供了更好的電氣性能並降低了成本。

圖3

Apple 憑藉其 Apple M1 Ultra 組件也進入了先進封裝市場,該組件使用本地硅中介層連接兩個處理器,將這項技術標記為超融合(ultra-fusion)。這種新穎的封裝工藝,包括芯片優先工藝(chip-first)和最後再分配(redistribution last)工藝,這也正是台積電的 InFO-L 工藝。該組件中使用的 LPDDR5 內存並未直接與處理器芯片互連,而是僅集成在封裝基板級別。

面對先進封裝縮放和互連方面的不同挑戰,混合鍵合已被引入作為各種半導體組件的封裝解決方案。

2022年,AMD還首創了V-Cache技術。它通過使用芯片到晶圓混合鍵合將緩存芯片連接到處理器來使用額外的緩存。這種使能技術允許高速緩存的垂直堆疊,以改進互連、減少鍵合間距並加快處理器內核對高速緩存的訪問。一旦混合鍵合良率得到優化,該工藝將為 3D 封裝提供更有前途的解決方案。

台積電在覆蓋前端和後端方面發揮着至關重要的作用,因為它具有製造用於最新處理器芯片的先進節點的代工能力,並提供 OSAT 無法提供的先進和複雜的後端服務。異構解決方案使具有不同功能的多個小芯片和來自不同製造工藝流程的芯片能夠集成到一個封裝中。主要目標是提供一種具有成本效益的集成方案,同時具有改進的性能、更高的傳輸速度和更低的功耗。

對設備和材料的要求

先進封裝設備與現有平台一樣多種多樣,服務於所有級別的互連,即在 Si 芯片(或小芯片)、Si 光子芯片、佈線或再分佈層 (RDL:redistribution layers) 級別。當中還包括如嵌入式橋接器或有機中介層、Si 中介層、IC 基板和高級印刷電路板 (PCB)在內的嵌入式佈線。在每個級別,我們都看到了減小互連間距和線間距 (L/S:line space) 的趨勢。製造這種互連的複雜性來自於形成它們的各種互連形狀和材料。互連類型、製造方法和使用的設備可以根據基板類型(晶圓或面板)和材料(Si、有機、玻璃)進行區分。

晶圓級封裝 (WLP) 設備相對完善。該設備不斷優化,以應對清潔和温度控制、高縱橫比特性、增加的粗糙度、翹曲控制以及對封裝中各種材料的考慮等挑戰。

硅芯片頂部的佈線以及硅通孔 (TSV) 均採用薄膜技術製造。對於寬鬆的 L/S,可以使用成熟的 MEMS 類型的設備,滿足core-FO、扇入、倒裝芯片和低端硅中介層的製造需求。對於更嚴格的 L/S,來自領先設備製造商的前端 300 毫米設備用於製造 BEOL 佈線、TSV 或用於高端硅中介層、硅橋接芯片、3D 堆棧存儲器和 3D SoC。WLP FO(HD 和 UHD)考慮了略有不同的方法,其中 RDL 或通模通孔(TMV:Through-Mold-Vias)被製造到環氧模塑料 (EMC:Epoxy Mold Compound)。

佈線完成後,芯片通過混合鍵合較大的焊料凸塊( bigger solder bumps)、較小的銅柱( smaller Cu pillars)、微凸塊(microbumps)或最小的直接銅焊盤(smallest direct Cu pad進行互連。其中,混合鍵合是設備和材料供應商在芯片和晶圓處理、鍵合後光刻、沉積、減薄和平面化、蝕刻和等離子切割以及混合互連核心方面的技術轉折點。

面板級封裝 (PLP) 設備和材料供應鏈更為複雜,通常使用定製設備在 EMC、有機面板、味之素積層膜(ABF)和玻璃之上互連。PLP 可以使用減材( subtractive)或增材(additive)工藝,其中設備優化通常受到表面貼裝技術 (SMT)、半導體和平板顯示器行業的啟發,以解決非對稱翹曲、更厚的基板、塗層或沉積的均勻性和減薄、粗糙度增加以及處理低温材料等挑戰。此外,由於缺乏適用於嚴格 L/S 的面板處理計量和檢測工具,PLP 過程控制很困難。IC 基板和先進的 PCB 面臨互連間距減小的挑戰,我們看到從 SMT 到薄膜的轉變技術。對於嵌入式橋接器的拾取和放置以及層壓到有機面板中的互連間距變得更加嚴格,RDL-first 用於 2.3D 有機中介層或 Chip-last FO。

總而言之,WLP 和 PLP 技術的改進與高端硅芯片的進步是互補的。因此,我們繼續看到許多令人振奮的發展。