本文來自格隆匯專欄:半導體行業觀察 作者: 杜芹DQ

1971年英特爾發佈的第一款CPU 4004內部晶體管數約有2300個,5年後,英特爾的Ponte Vecchio處理器將47個小芯片超過1000億個晶體管封裝到一個處理器中,過程中同時使用2.5D和3D技術。

2022年1月5日,AMD發佈首款3D堆疊的桌面處理器Ryzen 7 5800X3D,益於3D芯片堆疊,相比Zen2,Zen 3的平均性能提高了19%。

2022年3月4日,AI芯片公司Graphcore的Bow IPU芯片採用3D堆疊技術將AI速度提高40%。

2022年3月9日,蘋果發佈了計算機最高端處理器芯片M1 Ultra,將橫向排列的2枚芯片相互連接,配備了1140億個晶體管。

種種示例表明,2.5D/3D封裝技術正成為芯片性能提升的一大重要手段。通過以最低成本實現最高水平的硅集成和麪積效率,3D堆疊技術的重要性正在提高。全新的應用也不斷湧現,3D堆疊技術已成為滿足人工智能、機器學習和數據中心等應用程序所需性能的有利可圖的解決方案。

3D封裝成大勢所趨,技術挑戰不容小覷

隨着芯片微縮愈加困難,而市場對芯片高性能的追逐不減,業界開始探索在封裝領域尋求突破,所以這幾年,諸如2.5D/3D的先進IC封裝技術已經成為代工廠、封測廠、IDM、芯片設計廠商以及EDA廠商都競相關注的一環。

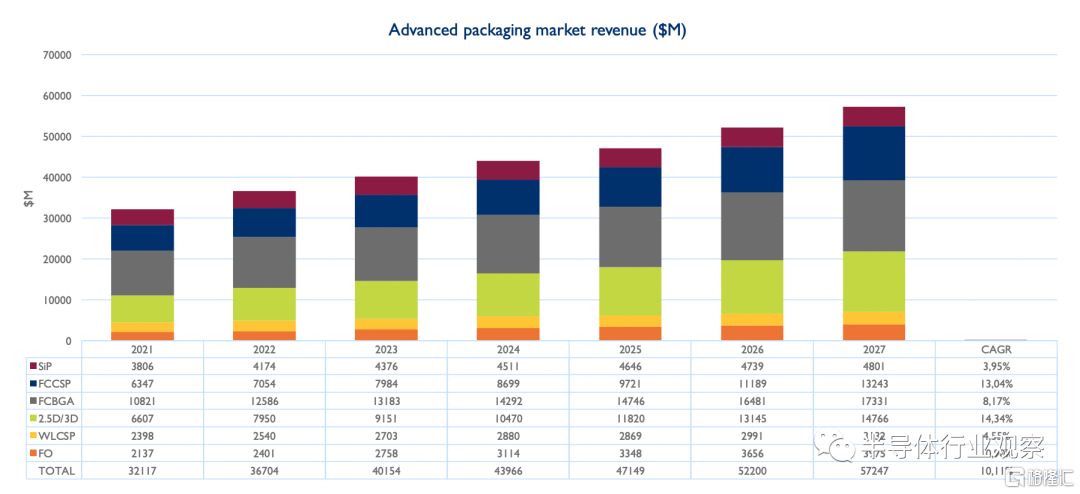

但由於成本的原因,高級封裝主要用於高端、面向利基市場的應用,如HPC等。3D封裝技術在HPC等主要的產業推動下迎來快速發展。據Yole 2022Q1發佈的先進封裝市場分析報吿,先進封裝市場的整體收入預計將以10.11%的年複合增長率增長,從2021年的321億美元增長到2027年的572億美元。而封裝的各個細分類別中,尤以2.5D/3D封裝市場的年複合增長率最大,從2021年的67億美元增加到2027年的147億美元,高達14.34%。

先進封裝市場營收及預測情況(圖源:Yole)

不僅僅是芯片製造過程的最後一步,封裝正在成為芯片創新的催化劑。3D封裝技術允許將不同的芯片如CPU、加速器、內存、IO、電源管理等像樂高積木一樣拼湊起來,其主要優勢是能實現更好的互連能效,減少訪問延遲。例如3D封裝技術允許在計算核心附近放置更多的內存,因此可以減少總的佈線長度,提高內存訪問帶寬,改善延遲,提升CPU性能,也因此大大提高了產品級性能、功耗和麪積,同時實現對系統架構的全面、重新思考。

如今,3D封裝已成為行業頂尖的芯片企業如英特爾、AMD、NVIDIA、蘋果等致勝的關鍵技術之一。雖然以3D IC為代表的異構封裝已經成為未來的重點發展方向,但落實新技術要面對不少棘手的問題。相比傳統的封裝技術,2.5D/3D IC異構封裝不僅僅是封裝廠技術的革新,更為原有的設計流程、設計工具、仿真工具等帶來挑戰。

首先,在進行2.5D/3D堆疊之後由於集成度的大幅度提升,發熱量變得更為集中,散熱是一大問題;其次,在芯片、中介層、基板膨脹、冷縮的過程中,需要保障機械應力的可靠性;再者, 芯片之間的高頻信號,需要滿足時序、信號完整性要求等問題;最後,芯片堆疊完成後,還需要測試上層芯片是否能正常工作,接線是否良好,堆疊過程中沒有被損壞等等。這些都是3D封裝需要面對的難題和挑戰。

3D封裝是全產業鏈共同配合的大業

因此,在這樣的背景下,3D封裝就需要供應鏈多個環節的支持,包括代工廠、封裝廠、EDA廠商、材料廠商等等。

在3D封裝方面,台積電、三星和英特爾這樣的晶圓代工廠是中流砥柱。台積電的“3D Fabric”、英特爾的“Foveros”以及三星的“X-cube”是三大代表的3D封裝技術品牌。根據市場研究公司 Yole Development 的數據,在2022年先進封裝的投資排名中,英特爾和台積電分別佔2022年全球先進封裝投資的32%和27%,三星電子排名第四(第三是日月光)。

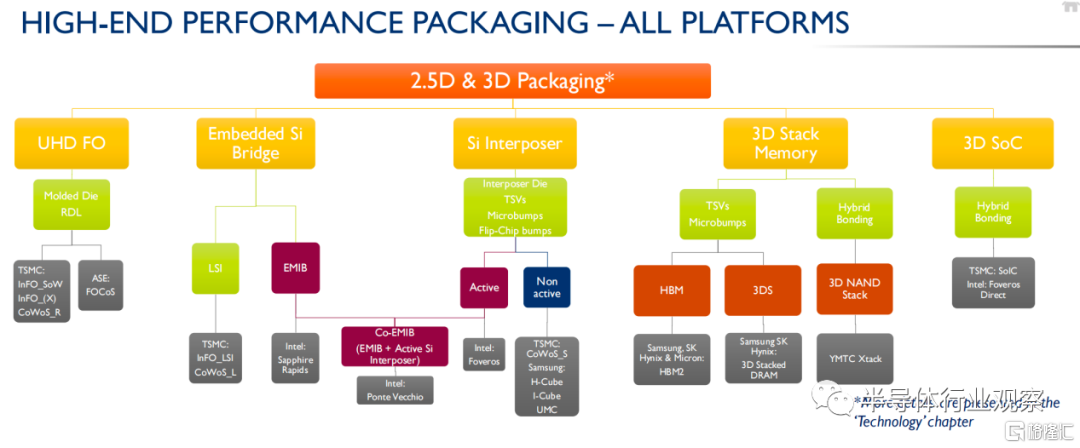

2.5D和3D封裝解決方案細分領域一覽(圖源:Yole)

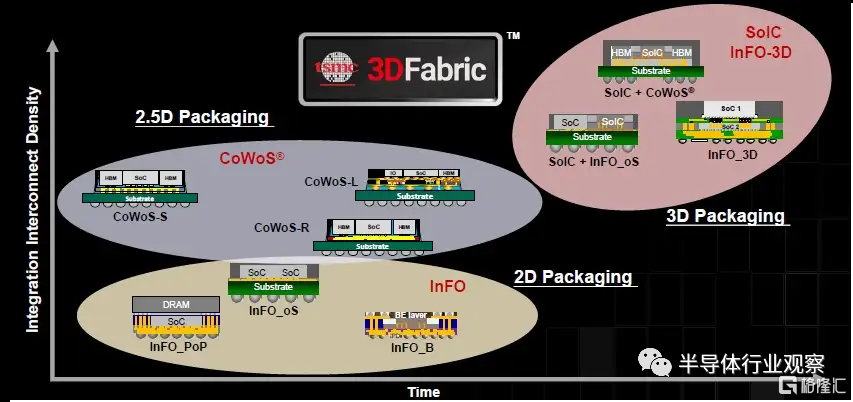

熟悉台積電的都知道,台積電將其SoIC(系統整合芯片)、InFO(整合型扇出封裝技術)、CoWoS(基板上晶圓上芯片封裝) 等2.5D和3D先進封裝與芯片堆棧技術整合成為了“3D Fabric”品牌。據台積電2022Q2財報説明會,目前台積電為HPC應用開發的3DIC、SoIC技術已經大部分開始被客户採用,台積電還在日本成立了3DIC中心,並於今年6月份舉行了開幕儀式。

圖源:SemiWiKi

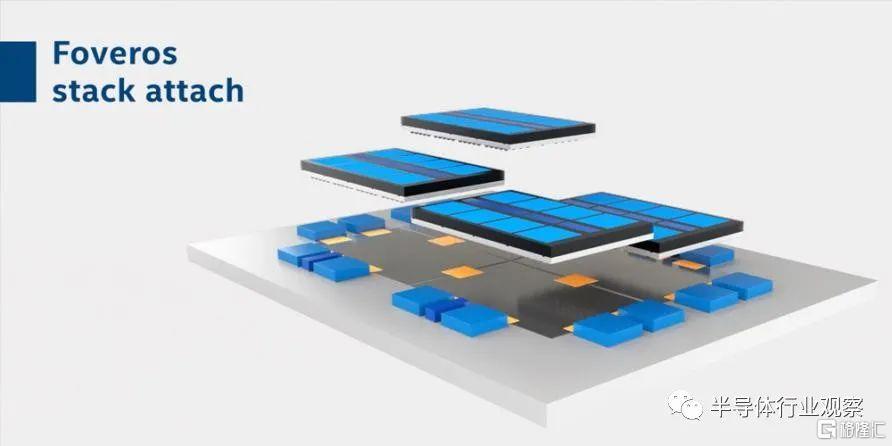

英特爾已將Foveros 3D封裝技術用於其Ponte Vecchio和Rialto Bridge GPU 以及 Agilex FPGA中,英特爾表示,採用 3D Foveros 封裝生產的芯片與標準單片(單芯片)芯片設計相比,在某些情況下具有極強的價格競爭力。英特爾於2021年5月宣佈將斥資35億美元用於新墨西哥Foveros晶圓廠。

圖源:英特爾

三星在3D封裝方面的核心競爭力來自於TSV和 PoP技術。2022年6月,三星成立半導體封裝工作組,顯示了三星對包括3D封裝在內的先進封裝的看重。

除了代工廠,傳統的封裝廠商也在積極向3D封裝技術過渡。封測龍頭日月光是較具實力的一員。2022年6月封測龍頭日月光推出VIPack 3D先進封裝平台,它是由六大核心封裝技術組成,包括日月光基於高密度RDL 的Fan Out Package-on-Package (FOPoP)、Fan Out Chip-on-Substrate (FOCoS)、Fan Out Chip-on-Substrate-Bridge (FOCoS-Bridge) 和Fan Out System-in-Package (FOSiP),以及基於硅通孔(TSV) 的2.5D/3D IC 和Co-Packaged Optics。其他封測廠如安靠、長電科技、通富微電等也在3D封裝領域蓄力。

此外,要製造3D芯片,需要在製造設備和原材料領域出現新的技術創新。關鍵的重要材料之一是用於多枚芯片連接的ABF載板。ABF載板是IC載板中的一種,ABF載板可做線路較細、適合高腳數高訊息傳輸的IC,具有較高的運算性能,主要用於CPU、GPU、FPGA、ASIC等高運算性能芯片。近幾年如Chiplet等技術的發展進步,對ABF載板的需求加大,另外也存在如何提高連接速度、改善散熱性和成本削減等課題。目前包括欣興、景碩、南電、Ibiden、Shinko、AT&S等主要ABF載板供應商都進行了一定的擴產。

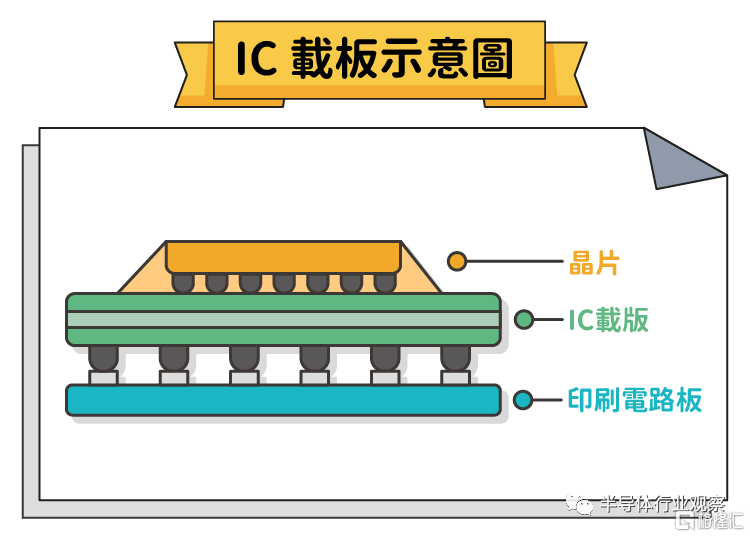

IC載板是一種介於IC半導體及PCB之間的產品,作為芯片與電路板之間連接的橋樑,可以保護電路完整,同時建立有效的散熱途徑。

圖源:stockfeel

但是3D IC封裝所面臨的難題,有時候單靠製造端是解決不了的,需要在芯片設計的一開始就提前規劃。3D IC封裝將不僅僅是“封裝”一個環節的事情,其更多體現在芯片和封裝的協同配合。

3D IC封裝最根本的挑戰來自於應用工具數據庫的轉變。芯片通用的GDS格式與PCB使用的Gerber格式有着根本上的差別,需要重新整合解決方案,以滿足先進封裝要求。此外,規模增長帶來的複雜性也是需要重點關注的問題。在做多晶粒(multi-die)時,面對日益龐大的系統,需要考慮能否承擔並驗證。還有一個值得注意的就是設計規劃,將多個芯片怎樣連接起來,用哪些工具去規劃,哪個文檔是正式“黃金參考”版本,都是需要事先確立的。只有確立了規劃,才能夠進行後續的設計、驗證。此時就凸顯出EDA工具的重要性。

而這些正是西門子EDA這樣的EDA廠商的價值所在,西門子EDA有一套成熟的端到端的EDA解決方案,結合其Xpedition, HyperLynx和Calibre技術,實現了快速有效的設計至GDS 籤核。例如,在芯片仿真驗證階段,結合西門子HyperLynx和Calibre系列工具,可以處理die、package和PCB仿真的協同問題,而不再是專注於單一設計領域;在芯片封裝設計佈局階段,西門子Xpedition Package Designer提供高效能的先進封裝技術支持,以及智能佈局功能,能提升封裝設計佈局效率並縮短佈局時間;在測試階段西門子EDA Tessent 工具平台基於工業分析,為3D IC提供集成並且流暢的EDA解決方案,通過靈活而完備的測試組合,實現提高測試覆蓋率、降低測試成本、追蹤良率問題的目標。

與此同時,EDA廠商與代工廠和封裝廠的協同合作也愈發重要。在這方面,西門子EDA已與台積電、三星以及日月光等積極展開合作,為他們提供生態上的支持。

其中,早在2020年,西門子EDA就獲得台積電“聯合開發3DIC設計生產力解決方案”年度OIP合作伙伴獎,2021年雙方在雲上 IC 設計以及台積電 3D 硅堆疊和先進封裝技術系列——3DFabric™方面達到了關鍵里程碑。再者,西門子EDA的高密度先進封裝解決方案已通過三星Foundry最新封裝工藝認證。西門子EDA還利用其Xpedition™ Substrate Integrator 軟件和 Calibre® 3DSTACK 平台與日月光推出新一代高密度先進封裝設計的支持技術,據日月光集團副總裁洪志斌博士表示:“雙方的合作使客户可以減少2.5D/3D IC和FOCoS的封裝規劃和驗證週期,在每一次設計週期中,大約可以減少30%到50%的設計開發時間。”

結語

隨着整個產業鏈逐漸日趨完善,並且不斷推出各領域新的支持的技術,如2.5D和3D封裝技術將成為接下來芯片性能提升過程的中流砥柱,也將是半導體產業的未來。3D封裝正在改變半導體世界,這一次將引起全產業鏈的變革。