本文來自格隆匯專欄:半導體行業觀察

晶體管微縮在 3nm 達到臨界點,納米片 FET 可能會取代 finFET 以滿足性能、功率、面積和成本 (PPAC) 目標。與此同時,人們正在評估2nm後銅互聯可能面對的一項重大架構變化,這一舉措將重新配置向晶體管供電的方式。

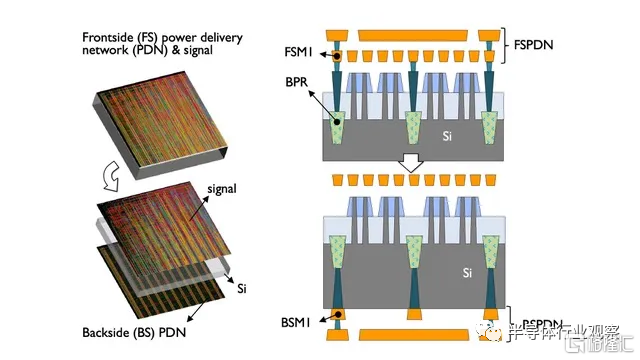

這種方法依賴於所謂的埋入式電源軌 (BPR) 和背面配電,讓正面互連來傳輸信號。英特爾宣佈將在其 20Å 代(相當於 2nm)使用其 PowerVia 結構,其他芯片製造商正在評估類似方案。

芯片製造商也可能會在 2nm 節點後儘快用釕或鉬替代一定程度的銅。其他更温和的變化將使用低電阻通孔工藝、替代襯墊和完全對齊的通孔方法來擴展銅鑲嵌互連。

大部分優化發生在鏈中的薄弱環節——接觸(金屬 0)、金屬 1 和通孔,其中 RC 延遲最有可能減慢芯片速度。Veeco首席技術官 Ajit Paranjpe 表示:“對於通孔填充,勢壘、種子和通孔金屬的保形沉積可能會被鈷(甚至釕)的無勢壘沉積和自下而上填充所取代。”

互連挑戰始於光刻技術,在整個 5nm 工藝中都採用了 EUV,這大大增加了成本。

EUV 和 BEOL 圖案化

在 7nm 節點 只有少數掩模層需要EUV光刻,但在 5nm(約 30nm 金屬間距)時,這會變為 15 到 18 層。在光刻中,由於不精確對齊的特徵,邊緣放置錯誤(edge-placement errors :EPE) 越來越受到關注。ASML研究員Robert Socha強調需要在 5nm 節點控制和減少 EPE 的影響。一個關鍵因素是覆蓋(overlay)誤差,5nm 節點的覆蓋預算僅為 2.5nm(5 個硅原子寬)。

KLA過程控制解決方案總監 Andrew Cross 表示:“我們已經看到 EPE 預算中的疊加元素隨着場內變化的增加而縮減得最快。” “這導致更高的光學覆蓋採樣、改進的覆蓋測量技術,以及在抗蝕劑顯影和蝕刻後使用基於 SEM 的覆蓋測量,這需要光學和電子束工具之間的協同作用。”

通孔優化

擴展銅技術的一個關鍵策略是消除銅通孔底部的阻擋金屬 TaN。實現這一點的一種方法是通過選擇性地沉積自組裝單層 (self-assembled monolayer:SAM) 薄膜,通過原子層沉積來沉積 TaN(ALD) 沿側壁,最後去除 SAM 並填充銅。在 IITC,TEL 使用雙鑲嵌集成描述了這樣一個過程,並比較了兩個自組裝單層(A 和 B)。在 TaN 阻擋層 ALD 之後,SAM 被蒸發,然後在通孔中進行銅化學沉積 (ELD)(見圖 1)。在通孔預填充之後,通過 CVD 在溝槽側壁上沉積釕襯墊,然後進行銅離子化 PVD 填充。使用 SAM B,結果顯示通孔底部沒有 Ta (EDX)。任何 SAM 的一個關鍵方面是它可以承受大約 350°C 的 ALD 工藝温度。

芯片製造商越來越多地將 SAM 工藝視為降低整體電阻和將銅鑲嵌工藝擴展到 2nm 節點的關鍵,無論是通過 CVD 還是旋塗。

另一種減少通孔底部阻擋金屬 (TaN) 體積的策略涉及從 PVD TaN 到 ALD TaN 的過渡,這將導致薄膜更薄、更連續。預計 ALD TaN 將在 5nm 節點上廣泛實施,可能採用 SAM 工藝。

圖 1:在這種自組裝單層 (SAM) 工藝中,在阻擋層和銅seed的 ALD 期間,薄膜會掩蓋通孔底部。然後通過在 325°C 下蒸發去除 SAM,然後填充銅。

完全對齊通孔 (FAV) 背後的理念

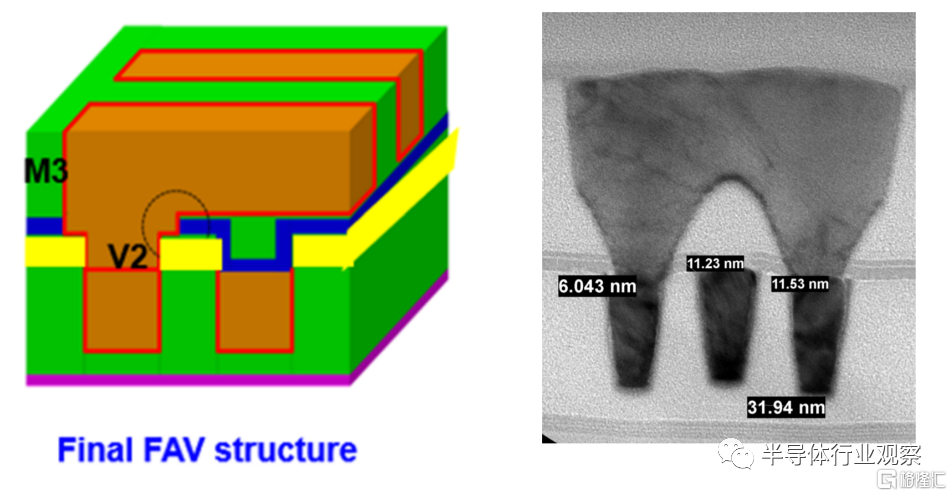

完全對齊通孔 (FAV) 背後的理念是減少通孔和線路之間的邊緣放置錯誤的影響,這會導致器件故障和長期可靠性問題。

自 32nm 節點以來,芯片製造商一直在採用自對準方法,使用 TiN 硬掩模將互連對齊到下面的水平。在完全對齊的過孔中,下面和上面的過孔被註冊。有兩種方法可以實現 FAV,通過從下面的線路蝕刻一些銅,然後圖案化並沉積通孔,或者通過在低 k 電介質上選擇性地沉積介電膜,然後進行通孔圖案化。

IBM和Lam Research的工程師提出了一種完全一致的方法,在簡化的整體工藝中使用選擇性電介質沉積 。據該小組稱,FAV 集成可以降低 70% 的電阻和增加 30% 的通孔接觸面積,同時保持通孔到線的可靠性(見圖 2)。使用銅和低 k 電介質 (SiCOH) 的 32nm 間距測試結構,該團隊使用濕化學方法使銅、襯墊和屏障凹陷。

“[凹槽蝕刻],當與蝕刻選擇性電介質cap結合使用時,可作為通孔引導圖案,減少覆蓋和臨界尺寸 (CD) 引起的邊緣放置錯誤,”IBM 表示。選擇性的氧化鋁膜通過 CVD 沉積在 low-k 上並用作部分蝕刻停止。該工藝成功的關鍵是高選擇性和有限的介電膜橫向過度生長,並且與標準 FAV 工藝相比沒有電阻降低或變化。IBM 表示,另一個優勢是金屬線的縱橫比較低(因為凹槽很淺),這有助於填充銅。

目前,尚不清楚完全對齊的方法會有多流行。“問題在於以什麼形式——在什麼水平和什麼間距上需要(完全對齊的通孔)?” Imec 研究員 Zsolt Tokei 問道。他指出,雖然凹槽蝕刻和選擇性沉積方法各有利弊,但關鍵問題是缺陷和提高新工藝的良率。即便如此,隨着 3nm 和 2nm 節點的 EPE 容差越來越小,像 FAV 這樣的方法可能會變得更加引人注目。

圖 2:使用選擇性沉積工藝為 5nm 節點製造兩級完全對齊的通孔。

選擇性沉積,也稱為區域選擇性沉積 (ASD),已經存在了幾十年,但直到最近幾年,它才邁出了從實驗室到晶圓廠的一步。對於 ASD,“殺手級應用”被證明是在銅線上沉積鈷帽(cap),與傳統的氮化硅帽相比,它能夠更好地控制電遷移。一些公司在 10nm 節點採用了該技術。連同銅下方的鈷襯墊(襯墊也稱為成核層或膠水層,因為它們能夠實現金屬粘附),鈷在此方案中包裹銅。

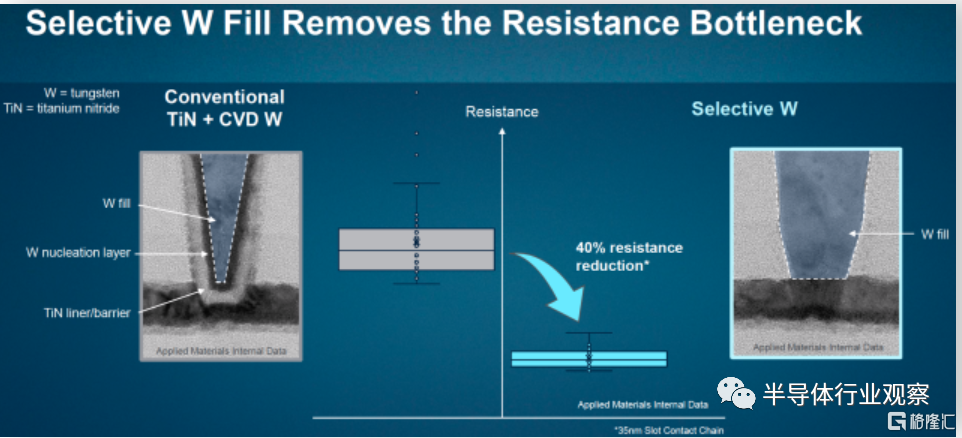

當目標是在金屬上沉積金屬或在電介質上沉積電介質時,選擇性 ALD 工藝表現最佳。根據設備供應商的不同,可以使用不同的化學機制來保持沉積的選擇性並防止在不需要的地方沉積。對於接觸金屬化,選擇性鎢沉積可能會通過改進填充和完全消除 TiN 勢壘來顯着降低電阻率(見圖 3)。通過消除側壁阻擋層和襯裏,選擇性鎢還允許清潔的金屬對金屬界面,以降低整體電阻。據應用材料公司稱,電阻降低 40% 是可能的。

圖 3:選擇性鎢自下而上填充提供了消除阻擋層和襯墊層、改善接觸和電阻的途徑。

鈷和鎢

在 14nm 或 10nm 技術節點之前,鎢一直是與金屬/多晶硅柵極以及晶體管上的源極和漏極硅化物區域進行電接觸的主要材料。近年來,鈷觸點採用了薄的 TiN 勢壘。同樣在線路或通孔中,更薄的勢壘以及更短的鈷平均自由程(10nm 對銅的 39nm)導致小線的電阻率更低(電子路徑更長,散射會增加淨電阻)。

英特爾是第一家在接觸級生產中使用鈷的公司,事實上,鈷的集成問題可能是英特爾 10nm 延遲問題的部分原因。儘管如此,幾家芯片製造商還是開始在觸點的生產過程中使用鈷,同時也將鈷用作銅互連的襯墊和封蓋材料。

襯墊金屬嚴重影響縮放互連線中銅的填充質量。在 IITC 的受邀演講中,IBM 通過 CVD 展示了使用新的襯裏鈷摻雜釕,相對於 36nm 金屬結構中的 CVD 鈷和 CVD 釕襯裏,提高了電遷移性能。IBM 確定新的襯裏具有更好的 EM 電阻,因為釕襯裏中的鈷抑制了由銅上的鈷帽引起的沿晶界的擴散。低温(250°C)迴流的 PVD 銅正成為密集互連的主流,而化學銅或 ECD 在全球範圍內使用。

下一個金屬:Ru還是Mo?

看來,在 1nm 節點(20nm 金屬間距),從銅到另一種金屬——釕或鉬——的變化將變得必要,至少在某些層面上是這樣。有趣的是,正在探索鉬和釕作為 3D NAND 閃存晶體管中鎢的字線替代品。

對於行業替代銅的選擇,縮放特徵的電阻是最重要的指標。同樣重要的是 EM 電阻,它與長期可靠性有關。釕、鉬和鈷的大部分優勢在於可以消除襯裏,從而提供更多的溝槽或通孔體積以供主要金屬佔據。可以使用迴流或激光退火來最大化晶粒尺寸。

“對於金屬線,釕是一種可能的替代品。雖然釕的體電阻率為 7 µohm-cm,但採用傳統濺射法沉積的 20nm 釕膜的有效電阻率大於 11 µohm-cm,”Veeco 的 Paranjpe 説道。“因此,正在探索替代方法,例如離子束沉積,它可以更好地控制晶體結構和晶粒尺寸。”

釕因其低電阻率、高熔點、耐酸腐蝕和極低的腐蝕潛力而作為下一代互連具有吸引力。

相比之下,鉬前體比釕便宜一個數量級。在 2nm 節點之前,兩者都不太可能需要。

“鉬肯定更便宜,所以如果你是工廠經理,你會更開心,”Imec 的 Tokei 説。“但如果你是一名工程師,你需要擁有所有可用數據來在材料之間做出決定,而我們還沒有完整的數據集。”

圖 4:通過在晶體管的隔離區域通過硅晶片構建一個導軌,晶體管功率傳輸(背面)與信號傳輸(正面)分離。

埋入式電源軌

BPR 和背面配電 (BPD) 的組合實質上採用了電源線和地線,這些線之前通過整個多層金屬互連進行佈線,並在晶圓背面為它們提供了一個專用網絡(見圖 4)。這減少了電壓 (IR) 降。

“在傳統互連中,您必須針對電源和信號優化金屬 0 和金屬 1,因此電源驅動高互連,而信號驅動細互連。你最終會做出權衡,這對任何一方來説都不是最優的,”Tokei 解釋道。“通過將電源佈線到背面,那裏會有高大、相對較寬的互連,而前面的信號和時鐘則有相對細長的電阻線,並且您顯着提高了佈線能力。” 他指出,正在對這些新結構的熱管理進行仔細評估。

BPR 和 BPD 存在許多挑戰,包括如何構建埋地電源軌,如何將配電網絡連接到電源軌,以及如何將電源從電源軌傳輸到晶體管。這些決定將決定集成方案以及最終的功率和擴展增益。

應用材料公司先進產品技術開發董事總經理 Mehul Naik 表示,製造挑戰將因方案而異,包括高縱橫比金屬填充、金屬和電介質選擇,以及通過背面研磨和 CMP 減薄晶圓。

英特爾宣佈將在其 20Å 代 (2nm) 上使用其 PowerVia,其目標是在 2024 年實現大批量生產。半導體工程與英特爾的高級副總裁兼技術開發總經理 Ann Kelleher 討論了 PowerVia,並詢問如何它不同於正在開發的其他方法。“在最高級別,埋藏的電力軌道是相同的總體主題,”Kelleher 説。“但是,它的實現方式有所不同。我們將功率從晶圓背面傳送到晶體管。Buried Power Rail 基本上是從前端獲取它,所以你有不同的架構來實現它。這是關鍵的區別。”

值得注意的是,英特爾的 PowerVia 似乎在觸點處連接,而 Imec 的電源軌嵌入在 STI(淺溝槽隔離)中。

Lam Research的計算產品副總裁 David Fried將埋地電力軌方法比作房屋的地下室。“如果你用地下室的比喻,每邊都需要一個樓梯間,”他説。“您現在可以從兩側訪問一樓的物品,而不僅僅是一個。當您可以從下方或上方訪問晶體管時,這可以打開一個全新的設計維度。這是一個巨大的變化。”

雖然這種轉變為在晶圓正面和背面構建晶體管需要許多工藝和設計創新,但背面電源仍將採用平面逐級構建這一事實建立在現有的行業知識之上。

“這是我相當看好的技術之一,”Fried説。“創新是困難的和多方面的,但它們的核心是經過驗證的。因此,埋入式電源軌只是三維流上的另一個二維層次。它仍然是平面處理,因此它與我們已經做的一切相似。將其組合在一起並使其發揮作用確實非常困難,但其核心並不像其他一些選擇那樣具有革命性。”

將需要金屬化、電介質和 CMP 方面的工藝創新。“當您使用電源軌並將其連接到設備時,您如何確保接口足夠乾淨,以及如何減少傳輸中的功率損耗?預清潔和與無空隙低電阻率金屬的集成將非常重要,”應用材料公司的 Naik 説。“將需要高質量、低熱預算的電介質 (≤400°C),因為這些工藝發生在包括金屬化在內的前端設備製造完成之後。”

另一個關鍵是CMP。對於晶圓減薄,背面晶圓研磨後將進行 CMP 以減薄器件晶圓。“從良率的角度來看,CMP 的工作是確保所有傳入的非均勻性得到管理,以在低缺陷率的情況下實現所需的全球晶圓厚度均勻性,”Naik 説。

從晶圓減薄的角度來看,用於 HBM 內存的多芯片堆疊和現在用於邏輯的背面供電都將減薄至 10 微米,但人們對更薄的興趣極大。“高密度堆疊正在推動這種需求,設計人員想要比現在更薄的硅片。從需要某些東西的那一刻起,技術人員就會擴展能力,這就是芯片堆疊正在發生的事情,”Tokei 説。

結論

芯片製造商正在評估 5nm 及以後的許多工藝變化,包括通孔電阻優化、完全對齊的通孔、鈷帽和觸點,以及分離電源和信號線以釋放擁擠的互連層。半導體行業總是更願意進行逐步的工藝修改,而不是儘可能地進行大的材料和結構變化。

增強可靠性、消除通孔底部的屏障和完全對齊通孔的新型襯墊似乎是一種可行的解決方案。工程師們開始解決圍繞電源軌和背面處理的挑戰。選擇性沉積已進入鈷帽晶圓廠,並且可能會在未來的其他應用中獲得認可。