本文來自:芯東西,作者:高歌

IMEC專家詳解3nm晶體管結構,四大關鍵工藝步驟揭祕。

近期最新消息,隨着三星、英特爾、台積電、IBM等半導體廠商相繼發佈新晶體管結構的進展,半導體行業正處於晶體管結構轉變的前夜。

雖然芯片行業從不急於採用新的晶體管結構進行量產,但如果想要生產3nm或2nm製程的邏輯芯片,英特爾、三星、台積電等廠商必須從當前的鰭式場效應晶體管結構(FinFET)逐漸過渡到納米片結構(Nanosheets)。

堀口直人是IMEC(比利時微電子研究中心)邏輯CMOS微縮項目主管,曾在富士通實驗室和加州大學聖巴巴拉分校等機構任職。目前,堀口直人的研發重點就是2nm以下的CMOS器件。

以下是記者對堀口直人就3nm晶體管結構發展回顧的完整編譯。

IMEC邏輯CMOS微縮項目主管堀口直人

納米片結構:進一步增強驅動電流,兼具可變性

一直以來,為了追尋摩爾定律,半導體產業在微縮邏輯CMOS尺寸上做出了相當大的努力。一種主要的方法是通過減少金屬連線(或軌道)來降低單元高度(cell height),單元高度也就是每個單元的金屬線數量乘以金屬間距(metal pitch,即金屬連線的最小寬度+金屬連線之間的最小間距)。

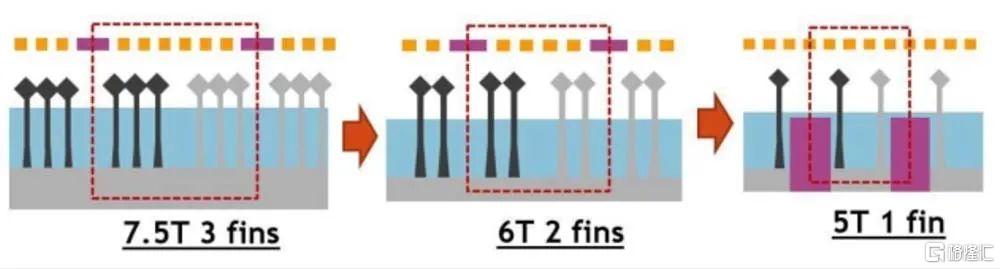

對於FinFET結構來説,通過將一個標準單元內的鰭片(Fin)的數量從3個減少到2個,就可以在性能上躍進一大步。

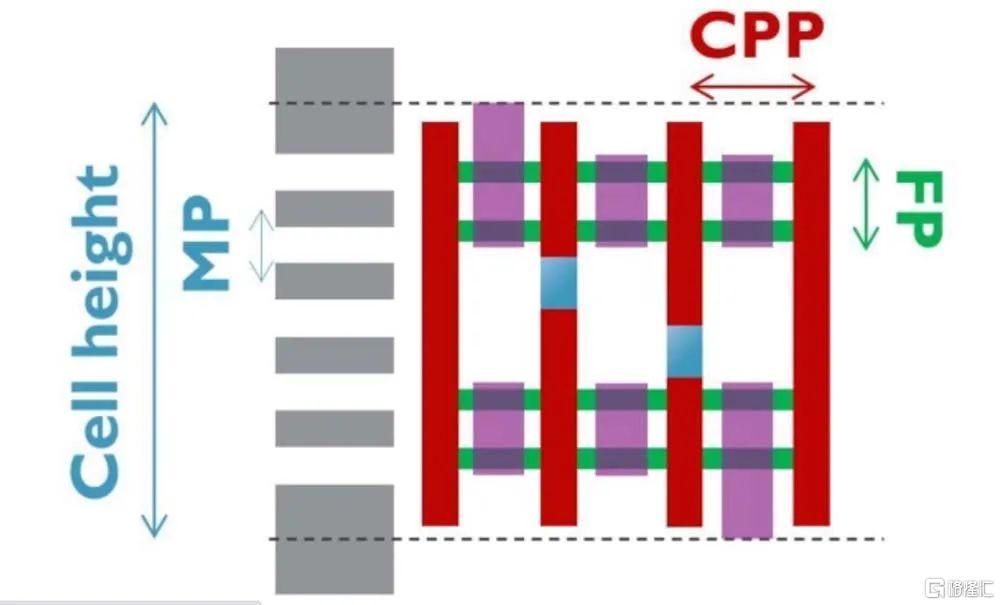

標準邏輯單元示意圖(CPP=接觸多晶間距,FP=鰭片間距,MP=金屬間距;單元高度=每個單元的金屬線數x金屬間距)

標準單元內單元高度中有幾條金屬連線則是一個重要指標,通常在單元高度範圍內有幾條金屬線就稱為幾T。隨着鰭片減少,單元高度逐漸變小,標準單元從7.5T變為了6T。然而這種縮小犧牲了內部的驅動電流和可變性,為了彌補這些性能的退化,鰭片在單元的高度微縮中也變得越來越高。

但是到了5T FinFET後,單鰭即便再高,其驅動電流卻很難隨之提升。通過垂直堆疊納米片狀導電溝道,納米片結構晶體管可以在標準單元內實現更大的有效溝道寬度。

通過這種方式,納米片結構的晶體管可以提供比鰭片更大的驅動電流,也是進一步微縮CMOS的基礎。同時納米片結構還允許可變的器件寬度,在設計中具備更高的靈活性。因為驅動電流有所增加,設計人員可以減少單元尺寸和電容,以降低每片之間的寄生電容。

標準單元微縮演進示意圖

4大關鍵工藝步驟實現納米片晶體管

除了驅動電流和可變性,納米片的環柵結構也優於FinFET結構。就像從平面MOSFET過渡到FinFET一樣,全柵納米片也伴隨着新工藝集成挑戰。

幸運的是,納米片基本算是FinFET的自然演變,許多為FinFET開發和優化的工藝模塊可以重複使用。這無疑促進了納米片結構在半導體行業中的應用,但也有很多工藝製程需要創新。IMEC確定了兩個結構不同的4個關鍵工藝步驟,需要進行創新。

第一,納米片結構使用外延生長的多層Si和SiGe來作為器件溝道。器件溝道使用生長材料以及2種材料之間的晶格常數不同,是納米片結構和傳統CMOS器件的一大區別。

在多層堆疊中,SiGe用作犧牲層(sacrifice),該層會在金屬柵極替換工藝步驟中的溝道釋放時移除。因為多層堆疊會以鰭的形式進行圖案化,鰭片容易發生形變。

在2017 IEDM會議上,IMEC提出了一個關鍵優化:實施淺溝槽隔離(STI)襯裏,並在STI工藝步驟中使用低熱來抑制氧化引起的鰭片變形。這不僅能夠保持納米片形狀,也可以提高設備的直交流性能,即驅動電流和恆定功率下的速度增益。改進的交流性能可以轉化為環形振盪電路的較低門延遲。

第二,與FinFET不同的是,納米片結構需要一個內部隔離物(inner spacer),即一種額外的電介質,將柵極與源極/漏極隔離以降低電容。

內部隔離物的工藝中,橫向蝕刻工藝會使多層堆疊結構中的SiGe層外部凹陷,產生小空腔,需要半導體廠商使用電介質材料填充這些空腔。這就是納米片工藝流程中最複雜的工藝模塊“內部間隔集成(Inner spacer integration)”,它需要高蝕刻選擇性和精確的橫向蝕刻控制,包括IMEC在內的全球多個研究團隊解決了這一挑戰。

第三是納米片溝道釋放,即納米片相互分離的步驟。正如前文所述,這種釋放往往通過選擇性的蝕刻掉多層SiGe來實現。該工藝中,需要半導體廠商進行高度選擇性的蝕刻,簡單來説就是儘量多地將納米片間的Ge殘留物蝕刻掉,同時不要使Si變得粗糙。

這就需要研究人員控制靜摩擦,以減少納米片間的連接。IMEC對不同蝕刻工藝的研究為解決這一問題做出了較大貢獻。

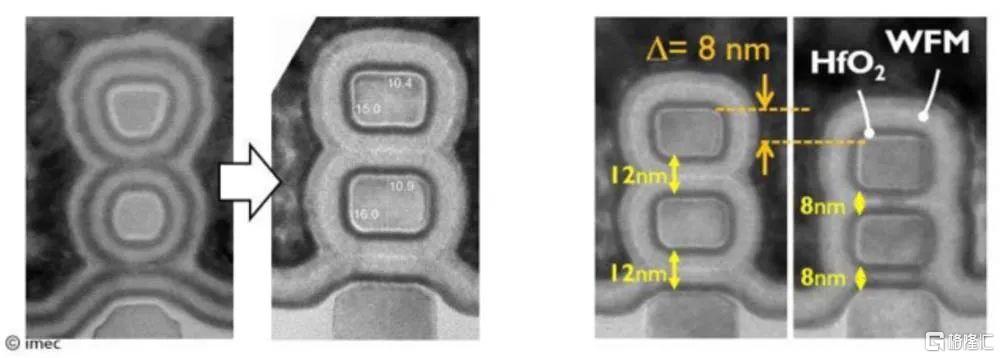

第四個則是替代金屬柵極(RMG)集成步驟,包括在納米片層周圍工作功能金屬(work function metal)的沉積和圖案化。

2018年,IMEC強調了引述可擴展工作功能今數的重要性,從而減少了納米片堆疊所佔的垂直空間。IMEC曾展示了將兩個垂直納米片之間的間隔物從13nm減少到7nm,並將芯片的AC性能提升了10%。

垂直堆疊環柵納米片晶體管的優化:改善納米片形狀控制(左),納米片垂直空間縮減分離(右)

Forksheet:增強器件直流性能,靜電控制不佳

如果想要進一步提升直流性能,最有效的方法使擴大溝道的有效寬度。但是,在納米片結構下,這變得非常困難。主要使因為n型和p型器件需要較大的空間,這使得在按比例微縮的單元高度上難以將納米片的有效寬度擴大。

2017年,IMEC首次公開提出Forksheet器件結構用來微縮SRAM,2019年IMEC又將這一器件結構用在邏輯芯片標準單元中。

和納米片結構相比,Forksheet在柵極圖案化之前,通過在p和n型器件間引入介電牆,實現更小的n、p間距,進一步增強了溝道的有效寬度以及直流性能。

這也讓研究人員可以利用較小的n、p間隔,將標準單元的單元高度從5T推進到4T。仿真結果顯示,Forksheet已比傳統納米片有10%的速度增益。這種性能提升的部分原因是由於柵極-漏極重疊較小而導致的(寄生)Miller電容減小。

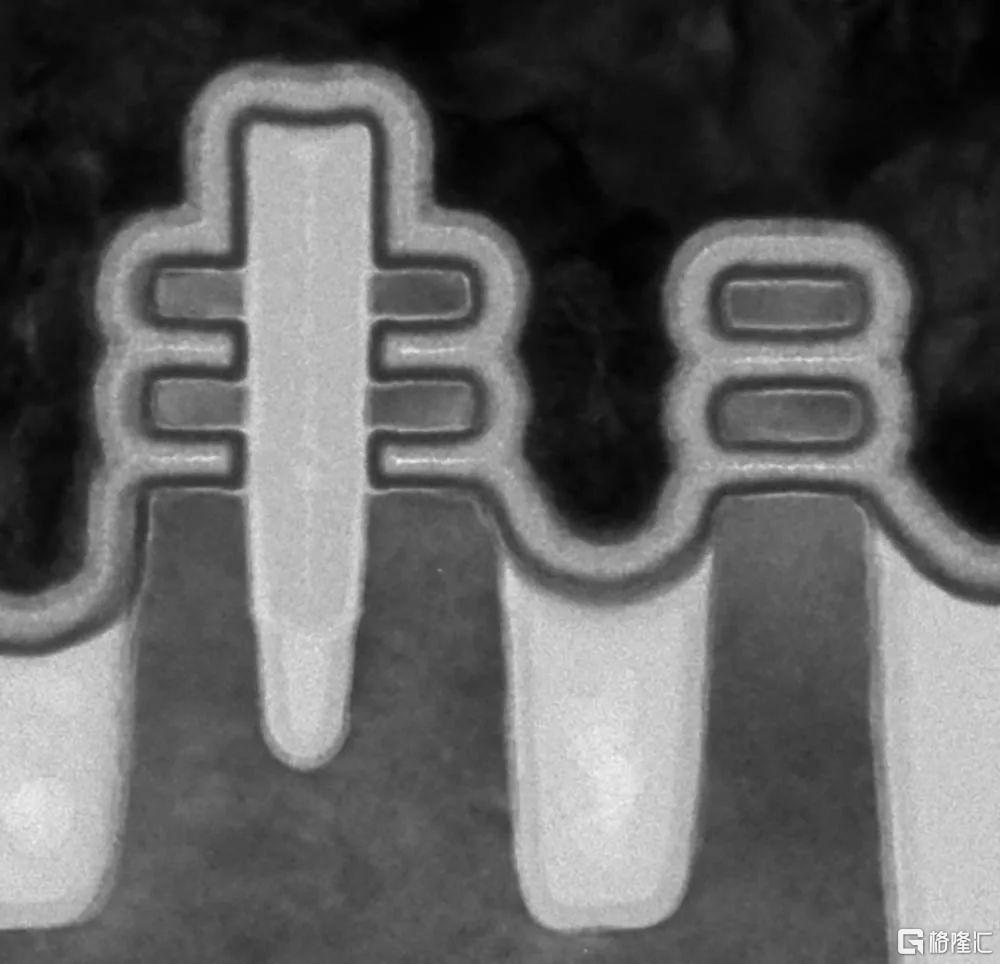

從工藝角度來看,Forksheet結構是從納米片演變而來,2者的關鍵區別在於電介質壁的形成、改進的內部隔離層、源極/漏極外延和替換金屬柵極步驟。

在VLSI 2021會議上,IMEC首次展示了使用300mm Forksheet集成的Forksheet場效應器件的電氣數據。雙工作功能金屬柵極可以在n-和pFET之間以17nm的間距集成,突出了Forksheet結構的關鍵優勢。

但是,Forksheet仍不完美。納米片結構的環柵在很大程度上改善了對溝道的靜電控制。Forksheet則採用了分叉形式的三門結構,似乎在靜電控制上有所退步。

集成在一起的納米片和Forksheet結構對比

CFET:CMOS器件最終結構,2種方案各有利弊

為了解決Forksheet的靜電控制問題,CFET隨即誕生。

CFET結構可以進一步最大化有效溝道寬度,其中n極和p極堆疊在彼此頂部,可以進一步減小單元面積,擴大溝道寬度,推動標準單元到4T及以下。

仿真證明,CFET對於邏輯芯片與SRAM尺寸微縮都有幫助。通過CFET,溝道可以製成鰭(n-fin on p-fin)或納米片(n-sheet on p-sheet)的形式。

而納米片形式的CFET完善了納米片結構的問題,是CMOS器件的最終結構。IMEC則在開發模塊和集成工藝上有着很大的貢獻,還量化了每個流程的功耗性能收益和複雜性。

從FinFET到CFET的晶體管結構演進過程

從處理角度來説,由於nMOS-pMOS垂直堆疊,CFET的結構較為複雜,有兩種可能的集成方案,分別是單片集成(monolithic)和順序集成(sequential),這兩種集成方案則各有利弊。

具體來説,單片CFET的成本較低,但是垂直集成十分複雜。單片CFET從底部溝道外延生長開始,然後是中間犧牲層的沉積,最後是頂部溝道的外延生長。當以納米片溝道為目標時,起始的底部和頂部溝道配置可以是Si鰭片或Si/SiGe多層堆棧的形式。

無論那種形式,堆疊都會導致非常高的垂直結構,這給鰭片、柵極、間隔和源/漏接觸的進一步圖案化帶來了關鍵的挑戰。例如,替換金屬柵極集成步驟由於需要用於n和p不同的工作功能金屬而更加複雜。在VLSI 2020上,IMEC率先展示了通過優化關鍵模塊步驟實現的單片集成CFET結構。

而相對來説,順序CFET的集成流程較為簡單。CFET順序集成由幾個模塊組成,首先對底層器件進行處理。然後使用介電到介電晶片鍵合技術,通過晶圓轉移在該層的頂部創建覆蓋半導體層。最後,集成頂層器件,連接頂柵和底柵。因為底層和頂層設備都可以用傳統的二維方式單獨處理,所以順序CFET可以靈活地集成用於n型和p型的不同溝道材料,進一步提升性能優勢。

但是作為新的方案,順序CFET也需要解決一些挑戰。第一個是涉及2個晶片之間鍵合介電氧化物厚度。過厚的氧化物會降低交流性能,但過薄的氧化物會產生鍵和缺陷風險。IMEC的薄鍵合氧化物工藝是解決氧化物厚度的一個方案,該工藝無鍵合空洞並且研發已經取得了進展。

順序CFET需要面對的第二個挑戰是晶圓轉移方法有熱預算限制,需要降低頂層工藝温度到500°C避免對底層器件產生負面影響,而該工藝此前需要900℃。

IMEC最近針對這兩個問題提出瞭解決方案,可以在較低的處理温度下使柵極堆疊保持可靠性。一種是通過低温氫等離子體處理鈍化硅氧化物夾層中的缺陷;第二種則是將界面偶極子Si引入溝道和HfO2柵極電解質之間,以抵消HfO2缺陷態和電荷載流子導帶之間的能量。

結語:先進製程玩家減少,競爭烈度或加劇

回顧從FinFET到CFET的研發過程,每一代結構的改進都伴隨着交流/直流性能的改進和標準單元高度的進一步降低。從處理的角度來看,納米片結構可以被認為是FinFET結構的進化步驟。然而,每種不同的納米片結構都面臨着特定的集成挑戰。

隨着芯片製程的不斷髮展,有能力繼續追求先進製程的玩家越來越少。IMEC作為芯片製程工藝的重要研發力量,有力地推動了芯片製程的微縮。此前,IMEC CEO曾接受採訪稱,要將芯片製程推進1nm以內。無論如何,人們對於更高性能、更少功耗的追求不會改變。屆時,先進製程的競爭可能會更加激烈。